Grundlagen der FPGAs: Was sind FPGAs und wofür sind sie erforderlich?

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2019-11-14

Optimale Verarbeitungslösungen werden oft durch Kombinationen von RISC, CISC, Grafikprozessoren und FPGAs, durch FPGAs allein oder durch FPGAs, die als Teil ihrer Struktur harte Prozessorkerne aufweisen, bereitgestellt. Viele Entwickler sind jedoch mit den Fähigkeiten von FPGAs, deren Entwicklung und deren Einsatzmöglichkeiten nicht vertraut. In diesem Artikel, Teil 1 einer 5-teiligen Serie, werden die Grundlagen von FPGAs diskutiert und Beispiellösungen von großen Anbietern vorgestellt. Teil 2, Teil 3, Teil 4, und Teil 5 wird sich auf die FPGA-Gerätefamilien und Design-Werkzeuge konzentrieren, die von Lattice Semiconductor angeboten werden, Microchip, Altera, und Xilinx.

Entwickler suchen stets nach Möglichkeiten, ihre Systeme als optimale Computerlösungen zu gestalten, die zu ihren Anwendungsanforderungen passen. In vielen Situationen erfordert eine optimale Lösung häufig den Einsatz feldprogrammierbarer Gate-Arrays (FPGAs), deren Fähigkeiten und Integrationsmöglichkeiten für viele Entwickler jedoch noch Neuland sind.

In diesem Artikel reißen wir kurz einige Szenarien an, in denen sich der Einsatz von FPGAs als vorteilhaft erweisen kann. Anschließend wird es um die Grundlagen ihrer Funktion gehen und werden einige interessante FPGA-Lösungen und Entwicklungskits vorgestellt.

Was spricht für den Einsatz von FPGAs?

Es gibt eine unglaubliche Fülle an Anwendungen, für die sich jeweils besondere Herangehensweisen anbieten. Dies beinhaltet standardmäßige Mikroprozessoren (MPUs) und Mikrocontroller (MCUs), standardmäßige Grafikprozessoren (GPUs), FPGAs und benutzerspezifische SoC-Komponenten (System-on-Ship). Was genau zu verwenden ist, erfordert eine genauere Betrachtung der Anwendungsanforderungen und -aspekte.

Bei der Arbeit mit modernsten Technologien (z. B. 5G-Basisstationen) müssen Entwickler beachten, dass die zugrunde liegenden Normen und Protokolle stets weiterentwickelt werden. Sie müssen also schnell und effizient auf Änderungen in Spezifikationen reagieren können, die sich ihrer Kontrolle entziehen.

Gleichermaßen müssen sie flexibel genug sein, um künftige Änderungen von Normen und Protokollen zu beachten, die nach dem Einsatz der Systeme im Feld verabschiedet werden. Sie müssen ferner auf unerwartete Fehler in der Funktionalität der Systeme oder Schwachstellen in der Systemsicherheit reagieren oder neue Funktionen hinzufügen können, um die Lebensdauer des Systems zu verlängern.

Die beste Leistung wird normalerweise mit einem SoC erreicht, dessen Einsatz jedoch kostspielig und zeitaufwendig ist. Außerdem sind in der Struktur des Chips integrierte Algorithmen mehr oder minder im Silizium „eingefroren“. In Anbetracht der obigen Herausforderungen kann sich dieser vorgegebene Mangel an Flexibilität schnell als Problem erweisen. Um also die goldene Mitte zwischen optimaler Leistung und Flexibilität zu finden, muss ein alternativer Weg gefunden werden. Auf diesem Weg liegen häufig FPGAs, Kombinationen aus Mikroprozessoren/Mikrocontrollern und FPGAs oder FPGAs mit in ihrer Struktur integrierten harten Prozessorkernen.

Was sind FPGAs?

Diese Frage kann nur schwer beantwortet werden, weil FPGAs verschiedene Bedeutungen für verschiedene Personen haben. Außerdem gibt es viele verschiedene Arten von FPGAs, die jeweils andere Kombinationen aus Fähigkeiten und Funktionen aufweisen.

Das Herzstück eines FPGA – quasi das bestimmende Merkmal der FPGAs – ist eine programmierbare Struktur, die sich als Array programmierbarer Logikblöcke darstellt (Abbildung 1a). Jeder dieser Logikblöcke enthält verschiedene Elemente (u. a. eine Look-up-Tabelle (LUT), einen Multiplexer und ein Register), die sich alle für bestimmte Anforderungen konfigurieren (programmieren) lassen (Abbildung 2).

Abbildung 1: Die einfachsten FPGAs beinhalten lediglich eine programmierbare Struktur und konfigurierbare GPIOS (a). In verschiedenen Architekturen wird diese grundlegende Struktur durch SRAM-Blöcke, PLLs und Taktmanager (b), DSP-Blöcke und SERDES-Schnittstellen (c) sowie harte Prozessorkerne und Peripheriebausteine (d) erweitert. (Bildquelle: Max Maxfield)

Abbildung 1: Die einfachsten FPGAs beinhalten lediglich eine programmierbare Struktur und konfigurierbare GPIOS (a). In verschiedenen Architekturen wird diese grundlegende Struktur durch SRAM-Blöcke, PLLs und Taktmanager (b), DSP-Blöcke und SERDES-Schnittstellen (c) sowie harte Prozessorkerne und Peripheriebausteine (d) erweitert. (Bildquelle: Max Maxfield)

Abbildung 2: Jeder programmierbare Logikblock enthält verschiedene Elemente (u. a. eine Look-up-Tabelle (LUT), einen Multiplexer und ein Register), die sich alle für bestimmte Anforderungen konfigurieren (programmieren) lassen. (Bildquelle: Max Maxfield)

Abbildung 2: Jeder programmierbare Logikblock enthält verschiedene Elemente (u. a. eine Look-up-Tabelle (LUT), einen Multiplexer und ein Register), die sich alle für bestimmte Anforderungen konfigurieren (programmieren) lassen. (Bildquelle: Max Maxfield)

Viele FPGAs nutzen LUTs mit 4 Eingängen, die für die Implementierung einer beliebigen Logikfunktion mit 4 Eingängen konfiguriert werden können. Zur besseren Unterstützung breiter Datenpfade, die in einigen Anwendungen zum Einsatz kommen, bieten bestimmte FPGAs sogar LUTs mit 6, 7 oder sogar 8 Eingängen. Der Ausgang der LUT wird direkt mit einem Logikblock-Ausgang und mit einem der Multiplexer-Eingänge verbunden. Ein weiterer Multiplexer-Eingang ist direkt mit einem Logikblock-Eingang (e) verbunden. Der Multiplexer kann so konfiguriert werden, dass einer dieser Eingänge ausgewählt wird.

Der Ausgang des Multiplexer fließt direkt in den Register-Eingang. Jedes Register kann so konfiguriert werden, dass es als Flip-Flop mit Flankensteuerung oder als vom Pegel abhängige Haltevorrichtung funktioniert (wobei jedoch angemerkt werden muss, dass die Verwendung einer asynchronen Logik in Form von Haltevorrichtungen in FPGAs nicht empfohlen wird). Der Taktgeber (oder die Aktivierung) jedes Registers kann für Aktiv-HIGH oder Aktiv-LOW konfiguriert werden. Auf ähnliche Art und Weise kann der aktive Pegel der Set/Reset-Eingänge festgelegt werden.

Diese Logikblöcke können als „Inseln programmierbarer Logik“ betrachtet werden, die einem „Meer programmierbarer Verbindungen“ treiben. Die Verbindungen können so konfiguriert werden, dass ein beliebiger Ausgang eines beliebigen Logikblocks mit beliebigen Eingängen anderer Logikblöcke verbunden werden kann. In gleicher Weise können die primären Eingänge des FPGA mit den Eingängen eines beliebigen Logikblocks verbunden und die Ausgänge beliebiger Logikblöcke zum Treiben der primären Ausgänge der Komponente genutzt werden.

Die Universal-Ein-/Ausgänge (GPIOs) werden auf Bänken (in Gruppen) umgesetzt. Die einzelnen Bänke können so konfiguriert werden, dass sie jeweils einen anderen Schnittstellenstandard wie LVCMOS, LVDS, LVTTL, HSTL oder SSTL unterstützen. Weiterhin kann die Impedanz der Eingänge sowie auch die Anstiegsrate der Ausgänge konfiguriert werden.

Auf der nächsthöheren Ebene enthält die FPGA-Struktur beispielsweise SRAM-Blöcke (sogenanntes Block-RAM (BRAM)), Phasenregelkreise (PLLs) und Taktmanager (Abbildung 1b). Blöcke für die digitale Datenverarbeitung (DSP) (DSP-Slices) können ebenfalls hinzugefügt werden. Diese beinhalten konfigurierbare Multiplikatoren und einen konfigurierbaren Addierer, der die Durchführung von MAC-Vorgängen (multiply-accumulate, multiplizieren-sammeln) ermöglicht (Abbildung 1c).

Eine weitere FPGA-Funktion, Hochgeschwindigkeits-SERDES-Blöcke, kann serielle Gigabit-Schnittstellen unterstützen. Es ist zu beachten, dass nicht alle FPGAs die gerade beschriebenen Funktionen unterstützen. Verschiedene FPGAs bieten verschiedene Kombinationen von Funktionen, die auf verschiedene Märkte und Anwendungen abgestimmt sind.

Die programmierbare Struktur in einem FPGA kann verwendet werden, um eine beliebige logische Funktion oder eine Gruppe gewünschter Funktionen bis hin zum Prozessorkern oder sogar mehrere Kerne zu implementieren. Wenn diese Kerne in einer programmierbaren Struktur implementiert werden, werden sie als „weiche Kerne“ bezeichnet. Andere FPGAs, die häufig als SoC FPGAs bezeichnet werden, beinhalten einen oder mehrere „harte Kernprozessoren“, die direkt auf dem Chip implementiert werden (Abbildung 1d). Diese harten Prozessorkerne können Gleitkommaeinheiten (FPUs) und einen L1/L2-Cache enthalten.

Die Funktionen von Peripherieschnittstellen wie CAN, I2C, SPI, UART und USB können auf ähnliche Weise als Softkerne in der programmierbaren Struktur implementiert werden. In vielen FPGAs sind sie jedoch als Hartkern auf dem Chip enthalten. Die Kommunikation zwischen Prozessorkernen, Schnittstellenfunktionen und programmierbarer Struktur erfolgt typischerweise über Hochgeschwindigkeitbusse wie AMBA und AXI.

Die ersten FPGAs, die 1985 von Xilinx auf dem Markt vorgestellt wurden, enthielten nur ein Array aus 8 x 8 programmierbaren Logikblöcken (keine RAM-Blöcke, DSP-Blöcke usw.). Die heutigen, hochmodernen FPGAs können dagegen Hundertausende Logikblöcke, Tausende DSP-Blöcke und RAM im Megabit-Bereich bieten. Insgesamt können sie Milliarden Transistoren enthalten, was zwischen 10 und 100 Millionen gleichwertigen Gates entspricht (z. B. NAND-Gates mit 2 Eingängen).

Alternative Konfigurationstechnologien

Die Bestimmung der Funktionen der Logikblöcke und die Leitung der Verbindungstechnik erfolgt mithilfe der Konfigurationszellen, die als 0/1-Schalter (aus/ein) dargestellt werden können. Diese Zellen werden auch für die Konfiguration des Schnittstellenstandards, der Eingangsimpedanz, Ausgangssteilheit usw. der GPIOs verwendet. In Abhängigkeit vom FPGA können diese Konfigurationszellen mithilfe einer der folgenden drei Technologien implementiert werden:

- Antifuse: Die Konfigurationszellen sind nur einmalig programmierbar (OTP), d. h. die Programmierung einer Komponente kann nicht rückgängig gemacht werden. Diese Komponenten kommen normalerweise eher in der Raumfahrt und in Anwendungen mit hoher Sicherheit zum Einsatz. Da sie in nur kleinen Mengen verkauft werden, ist ihr Preis ziemlich hoch, d. h. sie sind eine kostspielige Designoption.

- Flash: Wie die Antifuse-basierten Konfigurationszellen sind auch die Flash-basierten Zellen nicht flüchtig. Sie können jedoch im Gegensatz zu Antifuse-Zellen bei Bedarf neu programmiert werden. Die Zellen der Flash-Konfiguration sind strahlungsresistent und können daher bei Anwendungen in der Raumfahrt zum Einsatz kommen (wobei jedoch Änderungen an den oberen Metallschichten und ihrem Gehäuse erforderlich werden).

- SRAM: In diesem Fall werden die Konfigurationsdaten in einem externen Speicher aufbewahrt, aus dem sie immer dann geladen werden, wenn das FPGA aktiviert wird (gemäß Empfehlung im Fall dynamischer Konfigurationsszenarien).

Der Vorteil der FPGAs mit Antifuse- oder Flash-basierten Konfigurationszellen ist, dass sie sofort aktiv sind und wenig Strom verbrauchen. Ein Nachteil dieser Technologien besteht jedoch darin, dass sie neben dem zugrunde liegenden CMOS-Prozess zusätzliche Verarbeitungsschritte erfordern, um den Rest des Chips herzustellen.

Die Vorteile der FPGAs, deren Konfigurationszellen auf der SRAM-Technologie basieren, sind, dass sie mit demselben CMOS-Prozess wie der Rest des Chips hergestellt werden und eine höhere Leistung bieten, da sie der Antifuse- und Flash-Technologie normalerweise eine oder zwei Generationen voraus sind. Der wichtigste Nachteil besteht darin, dass die SRAM-Konfigurationszellen mehr Strom verbrauchen als ihre Antifuse- und Flash-Konkurrenz (im selben Technologieknoten) und anfällig für durch Strahlung verursachte Single-Event-Upsets (SEUs) sind.

Lange Zeit wurde aus diesem Grund davon ausgegangen, dass SRAM-basierte FPGAs für Anwendungen in der Luft- und Raumfahrt ungeeignet sind. Kürzlich wurden jedoch spezielle vorbeugende Strategien umgesetzt, die dazu führten, das SRAM-basierte FPGAs neben ihren Flash-basierten Verwandten in Systemen wie dem Mars Curiosity Rover anzutreffen sind.

Flexibilität durch den Einsatz von FPGAs

FPGAs kommen in vielen verschiedenen Anwendungen zum Einsatz. Sie eignen sich besonders für die Implementierung intelligenter Schnittstellenfunktionen, die Motorsteuerung, algorithmusbasierte Beschleunigung und Hochleistungsrechner (HPC), die Bild- und Videoverarbeitung, maschinelle Bilderfassung, künstliche Intelligenz (AI), maschinelles Lernen (ML), Deep Learning (DL), Radar, Strahlformung, Basisstationen und Kommunikation.

Ein einfaches Beispiel umfasst die Bereitstellung einer intelligenten Schnittstelle zwischen anderen Komponenten, in denen verschiedene Schnittstellenstandards oder Kommunikationsprotokolle zur Anwendung kommen. Betrachten wir ein bestehendes System, das einen Anwendungsprozessor enthält, der mit einem Kamerasensor und einem Anzeigegerät mit alten Schnittstellen verbunden ist (Abbildung 3a).

Abbildung 3: Ein FPGA kann eingesetzt werden, um eine intelligente Schnittstelle zwischen anderen Komponenten bereitzustellen, in denen verschiedene Schnittstellenstandards oder Kommunikationsprotokolle verwendet werden. Somit kann die Lebensdauer der bestehenden Designs der älteren Komponenten verlängert werden. (Bildquelle: Max Maxfield)

Abbildung 3: Ein FPGA kann eingesetzt werden, um eine intelligente Schnittstelle zwischen anderen Komponenten bereitzustellen, in denen verschiedene Schnittstellenstandards oder Kommunikationsprotokolle verwendet werden. Somit kann die Lebensdauer der bestehenden Designs der älteren Komponenten verlängert werden. (Bildquelle: Max Maxfield)

Nehmen wir jetzt an, dass die Entwickler des Systems den Kamerasensor und die Anzeigevorrichtung moderner gestalten möchten, sodass sie leichter und günstiger sind und weniger Strom verbrauchen. Das Problem besteht jetzt darin, dass eine oder beide dieser neuen Peripheriekomponenten möglicherweise einen modernen Schnittstellenstandard verwendet, der vom ursprünglichen Anwendungsprozessor (AP) nicht unterstützt wird. Oder aber sie unterstützen möglicherweise ein komplett verschiedenes Kommunikationsprotokoll wie die Mobile Industry Processor Interface (MIPI). In diesem Fall stellt der Einsatz eines FPGA, das mehrere I/O-Standards unterstützen kann, in Verbindung mit einigen MIPI-IP-Softkernen eine schnelle, kostengünstige und risikofreie Möglichkeit der Aktualisierung dar (Abbildung 3b).

Betrachten wir im nächsten Beispiel eine rechnungsintensive Aufgabe, beispielsweise die Durchführung der Signalverarbeitung, die für die Umsetzung eines Radarsystems erforderlich ist, oder die Strahlformung in einer Kommunikationsbasisstation. Herkömmliche Prozessoren mit einer von-Neumann- oder Harvard-Architektur eignen sich sehr gut für bestimmte Aufgaben, aber weniger gut für Aufgaben, bei denen dieselbe Vorgangssequenz immer und immer wieder durchgeführt wird. Dies liegt daran, dass ein einzelner Prozessorkern mit einem einzelnen Thread nur jeweils eine Anweisung ausführen kann (Abbildung 4a).

Abbildung 4: Im Gegensatz zu Mikroprozessoren, in denen jeweils nur eine Anweisung (nacheinander) ausgeführt werden kann, bieten mehrere Funktionsblöcke in einem FPGA die Möglichkeit der gleichzeitigen Ausführung. Die FPGAs können entsprechende Algorithmen zudem umfassend parallel implementieren. (Bildquelle: Max Maxfield)

Abbildung 4: Im Gegensatz zu Mikroprozessoren, in denen jeweils nur eine Anweisung (nacheinander) ausgeführt werden kann, bieten mehrere Funktionsblöcke in einem FPGA die Möglichkeit der gleichzeitigen Ausführung. Die FPGAs können entsprechende Algorithmen zudem umfassend parallel implementieren. (Bildquelle: Max Maxfield)

Da mehrere Funktionen gleichzeitig im FPGA ausgeführt werden können, können verschiedene Vorgänge „aufgereiht“ werden, wodurch ein deutlich höherer Durchsatz erreicht werden kann. Anstatt denselben Vorgang mit dem Prozessor beispielsweise zusätzlich 1000 Mal mit 1000 Datenpaaren durchzuführen, können diese umfassend parallel in einem einzigen Timerzyklus im FPGA ausgeführt werden, indem 1000 Addierer in der programmierbaren Struktur instantiiert werden (Abbildung 4b).

Wer stellt FPGAs her?

Diese Frage kann nicht abschließend beantwortet werden. Die beiden wichtigsten Hersteller von wirklich hochwertigen Geräten mit der höchsten Kapazität und Leistung sind Intel (die Altera erwarb) und Xilinx.

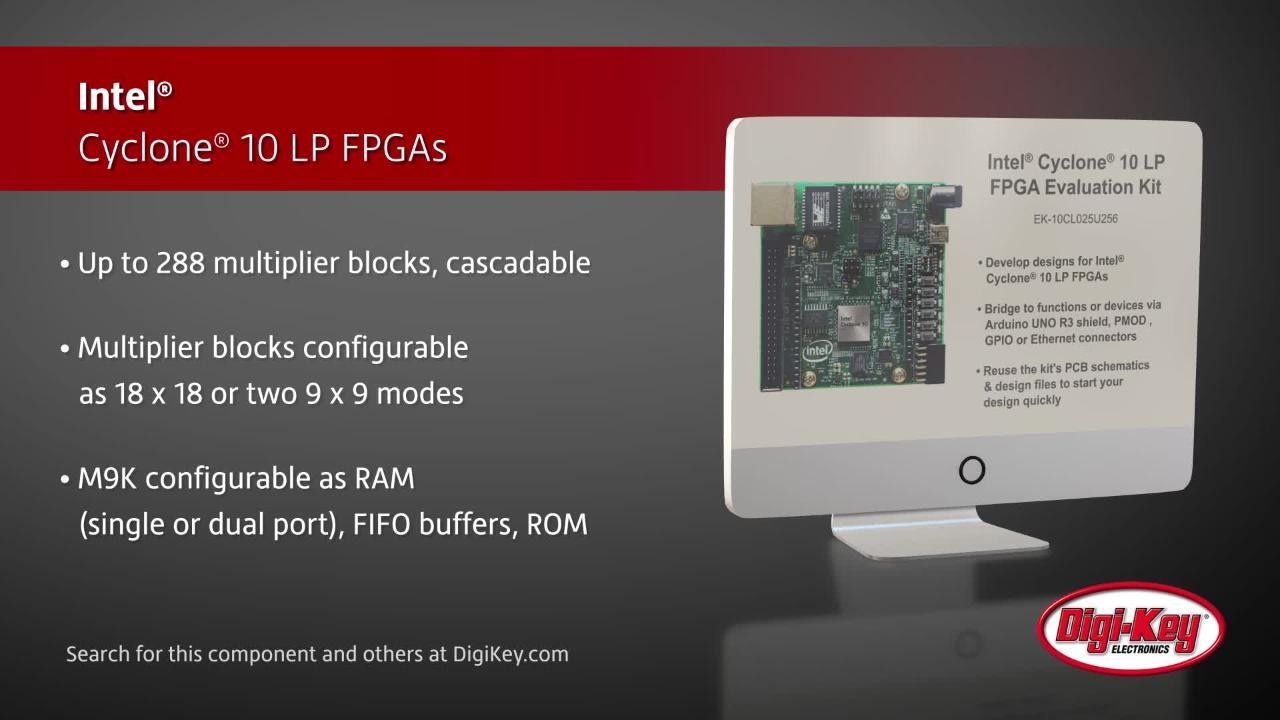

Das Angebot von Intel und Xilinx umfasst einfache FPGAs bis hin zu anspruchsvollen SoC FPGAs. Ein weiterer Anbieter, der sich fast ausschließlich auf FPGAs konzentriert, ist die Firma Lattice Semiconductor, die sich auf Anwendungen im unteren und mittleren Preissegment konzentriert. Zu guter Letzt bietet Microchip Technology (durch die Übernahme von Actel, Atmel und Microsemi) jetzt mehrere Familien kleiner bis mittelgroßer FPGAs und Low-End-Mitglieder der SoC-FPGA-Kategorie an.

Eine passende Komponente für eine Aufgabe auszuwählen kann sich aufgrund der großen Menge an Produktserien, die jeweils andere Ressourcen, Leistungen, Kapazität und Gehäusetypen aufweisen, schwierig gestalten. Aber sehen Sie selbst: Komponenten von Intel, Komponenten von Lattice Semiconductor und Komponenten von Xilinx.

Wie können FPGAs in die Entwicklung eingebunden werden?

Beim Design unter Verwendung von FPGAs nutzen Entwickler normalerweise eine Hardware-Beschreibungssprache wie Verilog oder VHDL, um den Zweck des Designs zu erfassen. Diese Beschreibungen können dann zunächst simuliert werden, um ihre Leistung zu bestätigen. Anschließend werden sie in ein Synthese-Tool übergeben, das die Konfigurationsdatei generiert, die für die Konfiguration (Programmierung) des FPGA verwendet wird.

Jeder FPGA-Hersteller bietet entweder eine selbst entwickelte Tool-Kette oder aber eine speziell angepasste Version eines Tools eines spezialisierten Anbieters an. Diese Tools werden über die Website des FPGA-Lieferanten verfügbar gemacht. Es kann auch vorkommen, dass kostenlose oder kostengünstige Versionen kompletter Tool-Suites angeboten werden.

Damit FPGAs häufiger von Software-Entwicklern eingesetzt werden, bieten einige FPGA-Lieferanten inzwischen HLS-Tools (High-Level Synthesis) an. Diese Tools übernehmen die Interpretation der algorithmischen Beschreibung des gewünschten Verhaltens, das sehr abstrakt in C, C++ oder OpenCL erfasst wird, Daraus werden die Eingaben generiert, die in das LLS-System (Lower-Level Synthesis) geleitet werden.

Entwickler, die dieses Gebiet näher erkunden möchten, können auf eine Vielzahl verschiedener Entwicklungs- und Evaluierungsboards zugreifen, die verschiedene Fähigkeiten und Funktionen bieten. Drei Beispiele hierfür sind: das Entwicklungskit DFR0600 von DFRobot mit einem Zynq-7000 SoC FPGA von Xilinx, das DE10 Nano von Terasic Inc. mit einem Cyclone V SoC FPGA von Intel und das Evaluierungsboard ICE40HX1K-STICK-EVN, das einen energiesparenden iCE40 FPGA von Lattice Semiconductor enthält.

Wenn Entwickler planen, eine FPGA-basierte PCIe-Tochterkarte für die Beschleunigung von Anwendungen zu verwenden, die auf einem X86 Motherboard laufen, sollten sie eine der Alveo PCIe-Tochterkarten (auch von Xilinx) in Betracht ziehen.

Fazit

FPGAs, Kombinationen aus Prozessoren und FPGAs oder FPGAs mit in ihrer Struktur integrierten harten Prozessorkernen stellen häufig die optimale Lösung dar.

FPGAs haben sich in den letzten Jahren stark weiterentwickelt und können viele Designanforderungen hinsichtlich Flexibilität, Verarbeitungsgeschwindigkeit und Leistung erfüllen, wodurch sie in einer Vielzahl von Anwendungen zum Einsatz kommen können.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.