Grundlagen von FPGAs - Teil 4: Erste Schritte mit Xilinx FPGAs

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2020-04-01

Anmerkung des Herausgebers: Optimale Verarbeitungslösungen werden oft durch Kombinationen von RISC-, CISC-, Grafikprozessoren und FPGAs, FPGAs allein oder durch FPGAs mit harten Prozessorkernen als Teil ihrer Struktur bereitgestellt. Viele Designer sind jedoch mit den Fähigkeiten von FPGAs, ihrer Entwicklung und ihrer Nutzung nicht vertraut. Teil 1 dieser mehrteiligen Serie bietet eine Einführung in FPGAs auf hohem Niveau; Teil 2 konzentrierte sich auf die FPGA-Angebote von Lattice Semiconductor; und Teil 3 konzentrierte sich auf die FPGA-Bausteinfamilien und Designwerkzeuge von Microchip Technology (von deren Tochtergesellschaft Microsemi Corporation). Hier, in Teil 4, werden die Komponenten und Werkzeuge von Xilinx besprochen. In Teil 5 werden die Angebote von Altera betrachtet.

Wie in Teil 1 erörtert, weisen FPGAs (Field-Programmable Gate Arrays) viele Eigenschaften auf, die sie zu einem unschätzbaren Rechenvermögen machen, entweder als Einzelgeräte oder in einer heterogenen Architektur, aber viele Designer sind mit FPGAs und der Integration dieser Bausteine in ihre Designs nicht vertraut.

Eine Möglichkeit, dieses Hindernis zu überwinden, besteht darin, sich eingehender mit den FPGA-Architekturen und den damit verbundenen Tools der wichtigsten Anbieter zu befassen; dieser Artikel befasst sich mit der Aufstellung von Xilinx.

Allgemeiner Überblick über die FPGA-Optionen

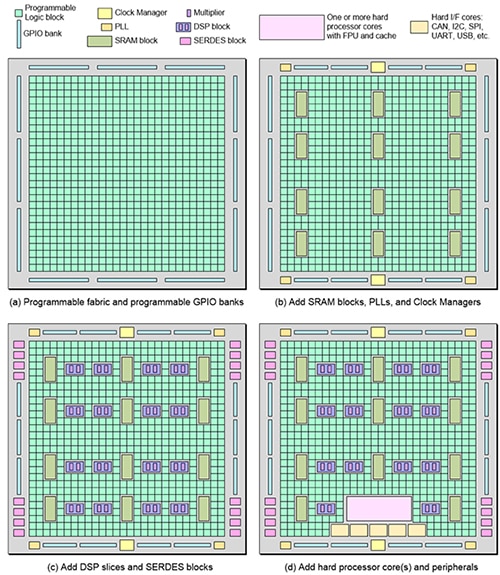

Es gibt viele verschiedene Arten von FPGAs, die jeweils andere Kombinationen aus Fähigkeiten und Funktionen aufweisen. Das Herzstück eines jeden FPGA ist seine programmierbare Struktur. Dies wird als eine Reihe von programmierbaren Logikblöcken, auch als Logikelemente (LEs) bezeichnet, dargestellt (Abbildung 1a). Der nächste Schritt in der FPGA-Fabric besteht darin, Dinge wie SRAM-Blöcke, so genanntes Block-RAM (BRAM), Phasenregelschleifen (PLLs) und Taktgeberverwalter zu integrieren (Abbildung 1b). Es können auch Blöcke für die digitale Signalverarbeitung (DSP-Blöcke) und Hochgeschwindigkeits-Serialisierer/Deserialisierer (SERDES-Blöcke) hinzugefügt werden (Abbildung 1c).

Abbildung 1: Die einfachsten FPGAs enthalten nur eine programmierbare Struktur und konfigurierbare Allzweck-IO (GPIO) (a); verschiedene Architekturen ergänzen diese grundlegende Struktur mit SRAM-Blöcken, PLLs und Taktmanagern (b); DSP-Blöcken und SERDES-Schnittstellen (c); und Hardprozessorkernen und Peripheriegeräten (d). (Bildquelle: Max Maxfield)

Abbildung 1: Die einfachsten FPGAs enthalten nur eine programmierbare Struktur und konfigurierbare Allzweck-IO (GPIO) (a); verschiedene Architekturen ergänzen diese grundlegende Struktur mit SRAM-Blöcken, PLLs und Taktmanagern (b); DSP-Blöcken und SERDES-Schnittstellen (c); und Hardprozessorkernen und Peripheriegeräten (d). (Bildquelle: Max Maxfield)

Die Funktionen von Peripherieschnittstellen wie CAN, I2C, SPI, UART und USB können als Softkerne in der programmierbaren Struktur implementiert werden. In vielen FPGAs sind sie jedoch als Hartkern auf dem Chip enthalten. In gleicher Weise können auch Mikroprozessoren als Softkerne in die programmierbare Struktur oder als Hartkerne in den Chip integriert werden (Abbildung 1d). FPGAs mit harten Prozessorkernen werden als System-on-Chip (SoC)-FPGAs bezeichnet. Verschiedene FPGAs bieten verschiedene Kombinationen von Merkmalen und Funktionen, die auf verschiedene Märkte und Anwendungen abgestimmt sind.

Es gibt eine Reihe von FPGA-Anbietern, darunter Altera (das von Intel übernommen wurde), Atmel (das von Microchip Technology übernommen wurde), Efinix, Lattice Semiconductor, Microsemi (das ebenfalls von Microchip Technology übernommen wurde) und Xilinx.

Alle diese Anbieter bieten mehrere Familien von FPGAs an; einige bieten SoC-FPGAs an, einige bieten Bausteine an, die auf Anwendungen der künstlichen Intelligenz (AI) und des maschinellen Lernens (ML) ausgerichtet sind, und einige bieten strahlungsresistente Bausteine an, die auf Umgebungen mit hoher Strahlung wie den Weltraum ausgerichtet sind. Die Auswahl einer passenden Komponente für die jeweilige Aufgabe kann sich aufgrund der großen Menge an Produktfamilien, die jeweils andere Ressourcen aufweisen, schwierig gestalten.

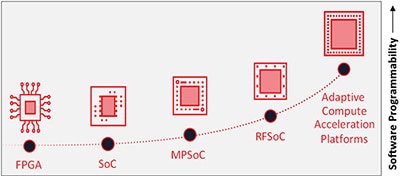

Einführung von Xilinx FPGAs, SoCs, MPSoCs, RFSoCs und ACAPs

Die Leistung und Fähigkeiten der programmierbaren Bausteine von Xilinx reichen von bescheiden bis extrem hoch. Von traditionellen FPGAs über SoCs (programmierbare FPGA-Fabric mit einem einzigen Hartkernprozessor), MPSoCs (programmierbare FPGA-Fabric mit mehreren Hartkernprozessoren), RFSoCs (MPSoCs mit RF-Fähigkeit) und ACAPs (Adaptive Compute Acceleration Platforms) (Abbildung 2).

Abbildung 2: Im Laufe der Zeit hat sich das Architektur-Portfolio von Xilinx von einfachen FPGAs, die nur eine programmierbare Fabric enthalten, zu SoC-Bausteinen entwickelt, bei denen die programmierbare Fabric mit einem Hardkernprozessor ergänzt wird, zu MPSoCs mit mehreren Prozessoren, zu RFSoCs mit RF-Fähigkeiten, zu der neuesten Generation von ACAPs, die auf Anwendungen wie AI ausgerichtet sind. (Bildquelle: Max Maxfield)

Abbildung 2: Im Laufe der Zeit hat sich das Architektur-Portfolio von Xilinx von einfachen FPGAs, die nur eine programmierbare Fabric enthalten, zu SoC-Bausteinen entwickelt, bei denen die programmierbare Fabric mit einem Hardkernprozessor ergänzt wird, zu MPSoCs mit mehreren Prozessoren, zu RFSoCs mit RF-Fähigkeiten, zu der neuesten Generation von ACAPs, die auf Anwendungen wie AI ausgerichtet sind. (Bildquelle: Max Maxfield)

Xilinx verfügt über ein so umfangreiches Produktportfolio, spricht so viele Marktsegmente an und bietet eine so breite Palette von Einsatzmethoden, dass es für jemanden, der neu in FPGAs ist, eine Herausforderung sein kann, das "große Ganze" zu verstehen.

Im Falle der Märkte, die Xilinx adressiert, aber nicht beschränkt ist auf, Datenzentren (Computer, Netzwerk, Speicher); Kommunikation (verkabelt, drahtlos); Luft- und Raumfahrt und Verteidigung; Industrie, Wissenschaft und Medizin (ISM); Test, Messung und Emulation (TME); und Automobil, Rundfunk und Verbraucher.

Bei den Bereitstellungsmethoden sind dies u.a. die von Xilinx so genannten Hardware Adaptable Devices, zu denen Chips, Evaluierungsboards und Entwicklungskits gehören, die Deployable End-Systems, zu denen System-on-Module (SoMs) und PCIe-Beschleunigerkarten gehören, und FPGA as a Service (FAAS), zu denen die Evaluierung und Nutzung von Xilinx-Technologien über führende Cloud-Anbieter wie Amazon Web Services (AWS), Alibaba.com und Nimbix.net gehört.

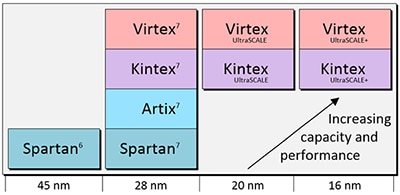

Eine Möglichkeit, die Xilinx-FPGA-Angebote zu kategorisieren, ist der Prozesstechnologie-Knoten (Abbildung 3).

Abbildung 3: Die FPGA-Angebote von Xilinx bieten ein umfassendes Multi-Knoten-Portfolio, um die Anforderungen einer Vielzahl von Anwendungen zu erfüllen. (Bildquelle: Max Maxfield)

Abbildung 3: Die FPGA-Angebote von Xilinx bieten ein umfassendes Multi-Knoten-Portfolio, um die Anforderungen einer Vielzahl von Anwendungen zu erfüllen. (Bildquelle: Max Maxfield)

Abhängig von der Zielanwendung können sich die Designer für ein kostengünstiges FPGA mit geringem Platzbedarf entscheiden, das an einem früheren Technologieknoten implementiert wird, oder im Falle einer hochmodernen Netzwerkanwendung z. B. ein Gerät mit hoher Kapazität, hoher Bandbreite und hoher Leistung wählen, das an einem neueren Technologieknoten implementiert wird.

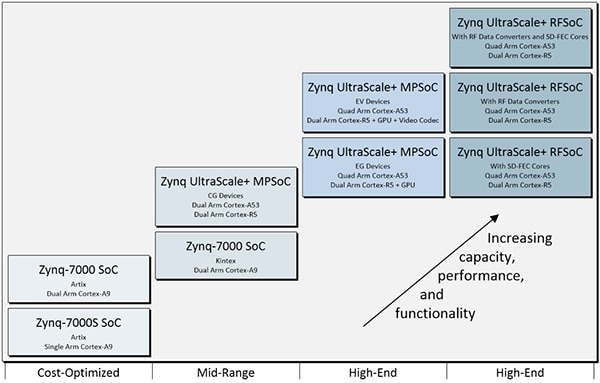

Für Designs, die einen oder mehrere harte Prozessorkerne (und andere gehärtete Funktionen wie GPUs, Codecs und Soft Decision, Forward Error Correction (SD-FEC)-Kerne) benötigen, bietet Xilinx ein Portfolio von Geräten unter dem Dachnamen Zynq an. Eine Zusammenfassung der Angebote von Zynq SoC, MPSoC und RFSoC ist in Abbildung 4 dargestellt. Diese Lösungssuite bietet Designern eine breite Palette von Funktionen, die die Optimierung von Leistung, Performance, Kosten und Markteinführungszeit erleichtern.

Abbildung 4: Die Xilinx SoC-, MPSoC- und RFSoC-Angebote integrieren die Softwareprogrammierbarkeit eines Prozessors mit der Hardwareprogrammierbarkeit eines FPGA und bieten Designern so Systemleistung, Flexibilität und Skalierbarkeit. (Bildquelle: Max Maxfield)

Abbildung 4: Die Xilinx SoC-, MPSoC- und RFSoC-Angebote integrieren die Softwareprogrammierbarkeit eines Prozessors mit der Hardwareprogrammierbarkeit eines FPGA und bieten Designern so Systemleistung, Flexibilität und Skalierbarkeit. (Bildquelle: Max Maxfield)

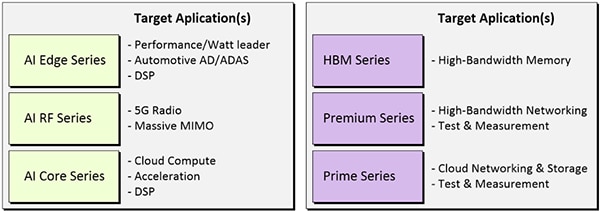

Die neuesten Angebote von Xilinx sind die Versal Adaptive Compute Acceleration Platform (ACAP) Geräte, die alle am 7-Nanometer (nm)-Prozesstechnologie-Knotenpunkt implementiert sind. ACAPs sind hochintegrierte Mehrkern-Computerplattformen, die sich an sich entwickelnde und unterschiedliche Algorithmen anpassen können. Sie sind auf der Hardware- und Softwareebene dynamisch anpassbar, um einer Vielzahl von Anwendungen und Arbeitsbelastungen gerecht zu werden. ACAPs sind um ein programmierbares Netzwerk-on-Chip (NoC) herum konzipiert und lassen sich sowohl von Hardware-Designern als auch von Software-Entwicklern leicht programmieren.

Zu den neuen Merkmalen der Versal-Geräte gehören intelligente Engines (eine riesige Anzahl von Vektorprozessoren für ML- und DSP-Arbeitslasten), ein programmierbarer NoC mit hoher Bandbreite, niedriger Latenz und geringem Stromverbrauch, der Terabytes von Daten bewegen kann, sowie ein integriertes Gehäuse, das eine verbesserte Leistung, Auslastung und Produktivität mit einer vordefinierten Kerninfrastruktur und Systemkonnektivität bietet.

Eine Übersicht über das Versal ACAP-Portfolio ist in Abbildung 5 dargestellt.

Abbildung 5: Xilinx Versal ACAPs sind hochintegrierte Mehrkern-Computerplattformen, die sich an sich entwickelnde und unterschiedliche Algorithmen anpassen können. ACAPs sind auf der Hardware- und Softwareebene dynamisch anpassbar, um einer Vielzahl von Anwendungen und Arbeitsbelastungen gerecht zu werden. (Bildquelle: Max Maxfield)

Abbildung 5: Xilinx Versal ACAPs sind hochintegrierte Mehrkern-Computerplattformen, die sich an sich entwickelnde und unterschiedliche Algorithmen anpassen können. ACAPs sind auf der Hardware- und Softwareebene dynamisch anpassbar, um einer Vielzahl von Anwendungen und Arbeitsbelastungen gerecht zu werden. (Bildquelle: Max Maxfield)

Wie im Abschnitt zu den Designwerkzeugen besprochen wird, ist ein Hauptunterscheidungsmerkmal der Versal-Geräte ein neuer Software-Stack, der sich an Datenwissenschaftler und Software-Ingenieure sowie an traditionelle Hardware-Designer richtet.

Es gibt jetzt eine Vielzahl von Xilinx-Geräten. Ein paar repräsentative Angebote wären ein Artix-7 FPGA, ein Kintex UltraScale FPGA, ein Kintex UltraScale+ FPGA, ein Zynq-7000 SoC Modul von Trenz Electronic GmbH und ein Zynq UltraScale+ MPSoC.

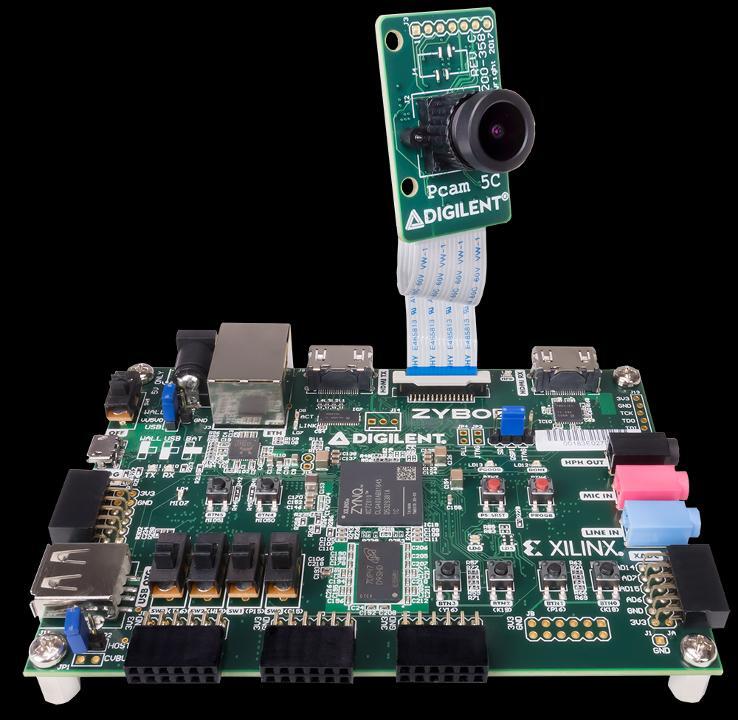

Ebenso gibt es eine Vielzahl von Evaluierungs- und Entwicklungsboards. Einige repräsentative Angebote wären ein Artix-7 FPGA Evaluation Board von Digilent, ein Kintex UltraScale FPGA Evaluation Board von Analog Devices, ein Kintex UltraScale+ FPGA Evaluation Board von Xilinx, ein Zynq-7000 SoC FPGA Evaluation Board von Digilent und ein Zynq UltraScale+ MPSoC FPGA Evaluation Board, ebenfalls von Xilinx.

Design und Entwicklung mit Xilinx FPGAs, SoCs und ACAPs

Ein Bereich, in dem sich Xilinx wirklich von der Konkurrenz abhebt, ist die Breite und Tiefe seiner Designwerkzeuge und -abläufe.

In Teil 1 dieser Serie über FPGAs haben wir festgestellt, dass die traditionelle Art und Weise, diese Bausteine zu entwerfen, darin besteht, dass die Ingenieure eine Hardware-Beschreibungssprache (HDL) wie Verilog oder VHDL verwenden, um die Absicht des Designs auf einer Abstraktionsebene zu erfassen, die als Register-Transfer-Ebene (RTL) bekannt ist. Diese RTL-Beschreibungen können zunächst simuliert werden, um zu verifizieren, dass sie wie gewünscht funktionieren. Danach werden sie an ein Synthesewerkzeug weitergeleitet, das die Konfigurationsdatei generiert, die zur Programmierung des FPGAs verwendet wird.

Der nächste Schritt in der Abstraktion besteht darin, die Absicht des Entwurfs mit einer Programmiersprache wie C/C++ oder einer speziellen Implementierung wie SystemC zu erfassen, bei der es sich um eine Reihe von C++-Klassen und Makros handelt, die eine ereignisgesteuerte Simulationsschnittstelle bereitstellen. Diese erleichtern die Simulation von gleichzeitigen Prozessen, die jeweils mit einfacher C++-Syntax beschrieben werden. Solche Beschreibungen können analysiert und profiliert werden, indem sie wie normale Programme ausgeführt werden. Danach werden sie an eine High-Level-Synthese-Engine (HLS) weitergeleitet, die RTL ausgibt, das in die reguläre Synthese-Engine eingespeist wird.

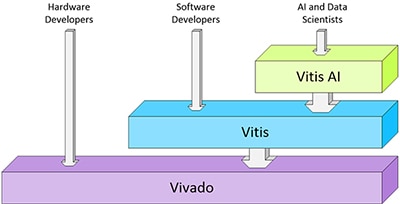

All diese Funktionen werden von den Vivado Design Suite HLx-Editionen übernommen, deren Ausgabe der Konfigurations-Bitstream ist, der in die Zielfunktionalität der FPGA-, SoC-, MPSoC-, RFSoC- oder ACAP-Geräte geladen wird. Neben der Möglichkeit für Hardware-Entwickler, C-basiertes Design und optimierte Wiederverwendung zu nutzen, bietet Vivado auch die Wiederverwendung von IP-Subsystemen, die Automatisierung der Integration und die beschleunigte Schließung des Designs (Abbildung 6).

Abbildung 6: Eine High-Level-Ansicht des Xilinx Vivado und Vitis Design-Tool-Stacks zeigt, wie die Benutzer mit den Werkzeugen auf den am besten geeigneten Abstraktionsebenen arbeiten können. Hardware-Designer arbeiten mit Vivado, Software-Entwickler mit Vitis und KI- und Datenwissenschaftler mit Vitis KI. (Bildquelle: Max Maxfield)

Abbildung 6: Eine High-Level-Ansicht des Xilinx Vivado und Vitis Design-Tool-Stacks zeigt, wie die Benutzer mit den Werkzeugen auf den am besten geeigneten Abstraktionsebenen arbeiten können. Hardware-Designer arbeiten mit Vivado, Software-Entwickler mit Vitis und KI- und Datenwissenschaftler mit Vitis KI. (Bildquelle: Max Maxfield)

Die nächste Abstraktionsebene wird von der Vitis Unified Software Platform unterstützt, die Software-Entwicklern die Möglichkeit bietet, nahtlos beschleunigte Anwendungen zu erstellen. Konzeptionell "steht über Vitis" Vitis AI, das es den KI- und Datenwissenschaftlern ermöglicht, auf der TensorFlow-Abstraktionsebene zu arbeiten. Vitis AI ist eine Entwicklungsplattform für KI-Inferenz auf Xilinx-Hardware-Plattformen, die sowohl Edge-Geräte als auch Alveo-PCIe-Karten umfasst. Es besteht aus optimierter IP, Tools, Bibliotheken, Modellen und Beispieldesigns und ist so konzipiert, dass das volle Potenzial für die AI-Beschleunigung auf Xilinx FPGA- und ACAP-Bausteinen ausgeschöpft wird.

Die KI von Vitis speist Vitis, das wiederum Vivado speist. Der wichtigste Aspekt aus Abbildung 6 ist, dass die Benutzer nur das "sehen", was sie "sehen" müssen. Das heißt, Hardware-Entwickler werden nur Vivado "sehen", Software-Entwickler nur Vitis "sehen" und KI- und Datenwissenschaftler nur Vitis KI "sehen". Auf diese Weise können die Benutzer mit den Werkzeugen auf den am besten geeigneten Abstraktionsebenen arbeiten.

Die Bereitstellung einer Tool-Suite wie Vitis für Software-Entwickler, die diese von der zugrunde liegenden Hardware isoliert, öffnet FPGAs für einen viel größeren Pool von Entwicklern. In ähnlicher Weise eröffnet die Bereitstellung einer Tool-Suite wie Vitis AI für KI- und Datenwissenschaftler, die es ihnen ermöglicht, sich auf ihre eigene Abstraktionsebene zu konzentrieren und sie von der zugrunde liegenden Software zu isolieren, FPGAs wieder einmal einer neuen Klasse von Entwicklern.

Mit der Bereitstellung dieser Fähigkeiten steht Xilinx an der Spitze eines branchenweiten Vorstoßes, FPGA-Werkzeuge auf immer höhere Ebenen der Design-Abstraktion zu heben, die es Entwicklern ermöglichen, die Fähigkeiten dieser Bausteine leichter zu nutzen und sie in ihre nächsten Designs zu integrieren.

Fazit

Optimale Verarbeitungsdesignlösungen werden oft durch Kombinationen von Prozessoren und FPGAs, durch FPGAs allein oder durch FPGAs mit harten Prozessorkernen als Teil ihrer Struktur bereitgestellt. Als Technologie haben sich FPGAs im Laufe der Jahre schnell entwickelt und sind in der Lage, viele Designanforderungen in Bezug auf Flexibilität, Verarbeitungsgeschwindigkeit und Leistung zu erfüllen, was sie für ein breites Spektrum von Anwendungen von intelligenten Schnittstellen bis hin zu maschineller Bildverarbeitung und künstlicher Intelligenz sehr nützlich macht.

Wie gezeigt, reicht das Angebot an programmierbaren Bausteinen von Xilinx in Bezug auf Leistung und Fähigkeiten von bescheiden bis extrem hoch. Sie reichen von traditionellen FPGAs über SoCs (programmierbare FPGA-Fabric mit einem einzigen Hartkernprozessor), MPSoCs (programmierbare FPGA-Fabric mit mehreren Hartkernprozessoren), RFSoCs (MPSoCs mit RF-Fähigkeit) bis hin zu ACAPs (Adaptive Compute Acceleration Platforms).

Um Designer bei der Erstellung von Entwürfen mit diesen Geräten zu unterstützen, bietet Xilinx eine Reihe von Werkzeugen an, die auf die Bedürfnisse von Hardware-Entwicklern (Vivado), Software-Entwicklern (Vitis) sowie KI- und Datenwissenschaftlern (Vitis AI) zugeschnitten sind.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.