Grundlagen von FPGAs - Teil 5: Erste Schritte mit Intel (Altera) FPGAs

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2020-05-07

Anmerkung des Herausgebers: Optimale Verarbeitungslösungen werden oft durch Kombinationen von RISC-, CISC-, Grafikprozessoren und FPGAs, FPGAs allein oder durch FPGAs mit harten Prozessorkernen als Teil ihrer Struktur bereitgestellt. Viele Designer sind jedoch mit den Fähigkeiten von FPGAs, ihrer Entwicklung und ihrer Nutzung nicht vertraut. Teil 1 dieser mehrteiligen Serie bietet eine Einführung in FPGAs auf hohem Niveau; Teil 2 konzentrierte sich auf die FPGA-Angebote von Lattice Semiconductor und Teil 3 konzentrierte sich auf die FPGA-Bausteinfamilien und Design-Tools von Microchip Technology (von ihrer Tochtergesellschaft Microsemi Corporation).Teil 4 tauchte tief in die Komponenten und Werkzeuge von Xilinx ein. Hier betrachtet Teil 5 die Angebote von Altera, das von Intel übernommen wurde und nun die Programmable Solutions Group bei Intel bildet (für den Rest dieses Papiers wird der Name Intel verwendet).

Wie in Teil 1 erörtert, weisen FPGAs (Field Programmable Gate Arrays) viele Eigenschaften auf, die sie zu einem unschätzbaren Rechenvermögen machen, entweder als Einzelkomponenten oder in einer heterogenen Architektur; viele Designer sind jedoch mit FPGAs und der Vorgehensweise bei der Integration dieser Bausteine in ihre Designs nicht vertraut. Eine Möglichkeit, dieses Hindernis zu überwinden, besteht darin, sich eingehender mit den FPGA-Architekturen und den damit verbundenen Tools der großen Anbieter zu befassen.

Allgemeiner Überblick über die FPGA-Optionen

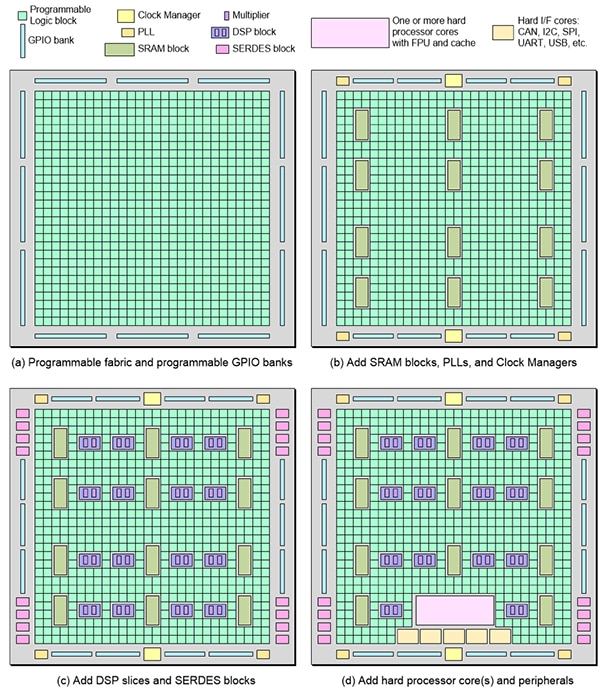

Es gibt viele verschiedene Arten von FPGAs, die jeweils andere Kombinationen aus Fähigkeiten und Funktionen aufweisen. Das Herzstück eines jeden FPGA ist seine programmierbare Struktur. Dies wird als eine Anordnung von programmierbaren Logikblöcken, auch als Logikelemente (LEs) bezeichnet, dargestellt (Abbildung 1(a)). Der nächste Schritt nach oben in der FPGA-Struktur besteht darin, Dinge wie SRAM-Blöcke, so genanntes Block-RAM (BRAM), Phasenregelschleifen (PLLs) und Taktmanager (Abbildung 1(b)) aufzunehmen. Digitale Signalverarbeitungsblöcke (DSP-Blöcke) (DSP-Slices genannt) und Hochgeschwindigkeits-Serialisierer/Deserialisierer-Blöcke (SERDES-Blöcke) können ebenfalls hinzugefügt werden (Abbildung 1(c)).

Abbildung 1: Die einfachsten FPGAs enthalten nur eine programmierbare Struktur und konfigurierbare Allzweck-IO (GPIO) (a); verschiedene Architekturen ergänzen diese grundlegende Struktur mit SRAM-Blöcken, PLLs und Taktmanagern (b); DSP-Blöcken und SERDES-Schnittstellen (c); und Hardprozessorkernen und Peripheriegeräten (d). (Bildquelle: Max Maxfield)

Abbildung 1: Die einfachsten FPGAs enthalten nur eine programmierbare Struktur und konfigurierbare Allzweck-IO (GPIO) (a); verschiedene Architekturen ergänzen diese grundlegende Struktur mit SRAM-Blöcken, PLLs und Taktmanagern (b); DSP-Blöcken und SERDES-Schnittstellen (c); und Hardprozessorkernen und Peripheriegeräten (d). (Bildquelle: Max Maxfield)

Die Funktionen von Peripherieschnittstellen wie CAN, I2C, SPI, UART und USB können als Softkerne in der programmierbaren Struktur implementiert werden. In vielen FPGAs sind sie jedoch als Hartkern auf dem Chip enthalten. In ähnlicher Weise können Mikroprozessoren als weiche Kerne im programmierbaren Gewebe oder als harte Kerne im Silizium implementiert werden (Abbildung 1(d)). FPGAs mit harten Prozessorkernen werden als System-on-Chip (SoC)-FPGAs bezeichnet. Verschiedene FPGAs bieten verschiedene Kombinationen von Merkmalen und Funktionen, die auf verschiedene Märkte und Anwendungen abgestimmt sind.

Es gibt eine Reihe von FPGA-Anbietern, darunter Intel (die Altera übernommen hat), Efinix, Lattice Semiconductor, Microchip Technology (die Atmel und Microsemi übernommen hat) und Xilinx.

Alle diese Anbieter bieten mehrere Familien von FPGAs an: einige bieten SoC-FPGAs an, einige bieten Bausteine an, die auf Anwendungen der künstlichen Intelligenz (AI) und des maschinellen Lernens (ML) ausgerichtet sind, und einige bieten strahlungstolerante Bausteine für Raumfahrtanwendungen an. Die Auswahl einer passenden Komponente für die jeweilige Aufgabe kann sich aufgrund der großen Menge an Produktfamilien, die jeweils andere Ressourcen aufweisen, schwierig gestalten.

Einführung von Intel-FPGAs und SoC-FPGAs

Die Leistung und Fähigkeiten der programmierbaren Bausteine von Intel reichen von bescheiden bis extrem hoch, von traditionellen FPGAs bis hin zu SoC-FPGAs (d.h. Bausteine, die programmierbare FPGA-Fabric mit einem oder mehreren gehärteten Prozessorkernen kombinieren).

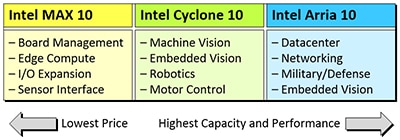

Intel hat fünf aktive FPGA-Familien in seinem aktuellen Produktportfolio, darunter die Max 10, Cyclone 10 und Arria 10 (Abbildung 2). Intel hat auch den extrem hochwertigen Stratix 10 und seine neueren, hochmodernen Agilex-Geräte.

Abbildung 2: Zielanwendungen und Märkte für drei der fünf FPGA-Familien von Intel - von den niedrigsten Kosten (max. 10) bis zur höchsten Kapazität und Leistung (Arria 10) - reichen von Board-Management und I/O-Erweiterung bis hin zu Embedded Vision und Militär/Verteidigung. Mit den Agilex-Geräten Stratix 10 und neuer wird die Leistung weiter gesteigert. (Bildquelle: Max Maxfield)

Abbildung 2: Zielanwendungen und Märkte für drei der fünf FPGA-Familien von Intel - von den niedrigsten Kosten (max. 10) bis zur höchsten Kapazität und Leistung (Arria 10) - reichen von Board-Management und I/O-Erweiterung bis hin zu Embedded Vision und Militär/Verteidigung. Mit den Agilex-Geräten Stratix 10 und neuer wird die Leistung weiter gesteigert. (Bildquelle: Max Maxfield)

Die Intel Max 10 FPGAs enthalten On-Chip-NOR-Flash-Speicher zur Aufnahme der FPGA-Konfiguration. Die anderen Produktfamilien verfügen über SRAM-basierte Konfigurationszellen und laden ihre Konfigurationen beim Einschalten von einem externen On-Board-Speichergerät oder von einer anderen Stelle im System (z.B. unter Kontrolle eines externen Prozessors). Mit Ausnahme der MAX 10-Familie sind alle anderen Intel-FPGA-Familien als FPGAs oder als SoC-FPGAs mit integrierten gehärteten Mikroprozessorsystemen erhältlich.

Zu den integrierten Funktionen der MAX 10-FPGAs gehören Analog-Digital-Wandler (ADCs) und Dual Configuration Flash, das die Möglichkeit bietet, zwei Bilder auf einem einzigen Chip zu speichern und dynamisch zwischen ihnen umzuschalten. MAX 10-FPGAs bieten außerdem Nios II-Softcore-Unterstützung für eingebettete Prozessoren, DSP-Blöcke und DDR3-Speicher-Controller (Soft Double Data Rate 3).

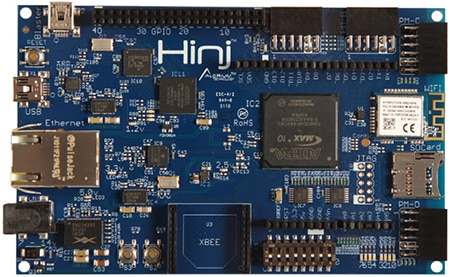

Ein repräsentativer Baustein aus dem MAX 10-Portfolio wäre der 10M16SCU169I7P mit 16.000 Logikelementen/Zellen, insgesamt 562.176 RAM-Bits und 130 Ein-/Ausgängen (I/O). Ein geeignetes Evaluierungsboard für den MAX 10 ist Intels EK-10M08E144. Ein weiteres ist das HINJKIT, ein FPGA IoT-Sensor-Hub-Entwicklungskit von Alorium Technology, LLC (Abbildung 3). Das HINJKIT ist von besonderem Interesse, weil sein MAX 10 FPGA den AVR-kompatiblen 8-Bit-Mikrocontroller von Alorium Technology enthält, wodurch das HINJKIT mit der Arduino-IDE verwendet werden kann. Die Karte bietet außerdem ein hohes Maß an Schnittstellenflexibilität für IoT-Trägerkarten, Module und Zubehör von Drittanbietern.

Abbildung 3: Das HINJKIT ist eine MAX 10-FPGA-Entwicklungsplattform von Alorium, die ein hohes Maß an Schnittstellenflexibilität für IoT-Trägerkarten, Module und Zubehör von Drittanbietern bietet. (Bildquelle: Alorium Technology)

Abbildung 3: Das HINJKIT ist eine MAX 10-FPGA-Entwicklungsplattform von Alorium, die ein hohes Maß an Schnittstellenflexibilität für IoT-Trägerkarten, Module und Zubehör von Drittanbietern bietet. (Bildquelle: Alorium Technology)

Intels Cyclone 10 GX FPGAs bieten 12,5 Gigabyte (Gbyte) Transceiver-basierte Funktionen, 1,4 Gigabit pro Sekunde (Gbit/s) Low-Voltage Differential Signaling (LVDS) und eine bis zu 72 Bit breite DDR3-SDRAM-Schnittstelle für Datenraten von bis zu 1.866 Megabit pro Sekunde (Mbits/s). Cyclone 10 GX FPGAs sind für Hochleistungsanwendungen mit hoher Bandbreite optimiert, wie z.B. industrielle Bildverarbeitung, Videokonnektivität und Smart Vision-Kameras.

Im Vergleich dazu sind die Cyclone 10 LP FPGAs für niedrige statische Leistung und kostengünstige Anwendungen wie E/A-Erweiterung, Sensor-Fusion, Motor-/Bewegungssteuerung, Chip-to-Chip-Überbrückung und Steuerung optimiert. Sowohl die GX- als auch die LP-Bausteinfamilien unterstützen die vertikale Migration, so dass Entwickler mit einem Baustein beginnen und zu einem späteren Zeitpunkt zu benachbarten Dichten übergehen können.

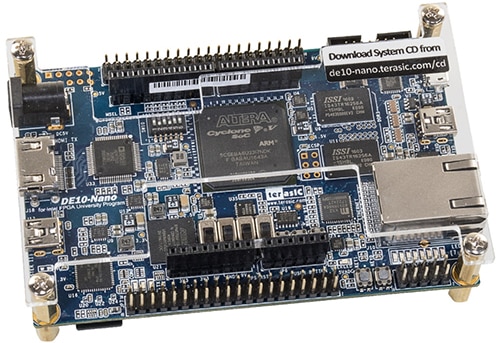

Ein repräsentatives Mitglied des Cyclone 10-Portfolios wäre der 10CL006YU256A7G mit 6.272 Logikelementen/Zellen, insgesamt 276.480 RAM-Bits und 176 E/A. Es gibt eine Vielzahl von verwandten Entwicklungs- und Evaluierungsboards und -modulen, darunter das P0496 DE10-NANO Cyclone V SE SoC Kit (Abbildung 4), das P0553 TSoM Cyclone V SE Evaluation Board (wiederum basierend auf dem Cyclone V SoC FPGA), und das P0581 TSoM Cyclone V SE FPGA Evaluation Board, alle von Terasic Inc. (Beachten Sie, dass das auf diesen Boards enthaltene Cyclone V FPGA eine frühere Generation der Cyclone 10-Familie ist).

Abbildung 4: Das kostengünstige Entwicklungskit P0496 DE10-NANO stellt eine robuste Hardware-Design-Plattform dar, die es Anwendern ermöglicht, mit Cyclone FPGAs zu experimentieren und zu evaluieren. (Bildquelle: Terasic Inc.)

Abbildung 4: Das kostengünstige Entwicklungskit P0496 DE10-NANO stellt eine robuste Hardware-Design-Plattform dar, die es Anwendern ermöglicht, mit Cyclone FPGAs zu experimentieren und zu evaluieren. (Bildquelle: Terasic Inc.)

Basierend auf der 20 Nanometer (nm)-Prozesstechnologie von TSMC kombinieren die Arria 10 Bausteine ein Dual-Core Arm Cortex-A9 MPCore Hard Processor System (HPS) mit einem programmierbaren Gewebe, das gehärtete Gleitkomma-DSP-Blöcke enthält. Die Arria 10-Geräte verfügen außerdem über eingebettete Hochgeschwindigkeits-Transceiver, Hardwarespeicher-Controller und IP-Controller (Protocol Intellectual Property), die alle in einem einzigen hochintegrierten Paket untergebracht sind.

Ein repräsentatives Gerät aus dem Arria 10-Portfolio wäre der 10AX022C4U19E3SG, mit 220.000 Logikelementen/Zellen, 13.752.320 RAM-Bits insgesamt und 240 E/A. Für die Entwicklung mit diesem FPGA ist eine geeignete Plattform das DK-DEV-10AX115S-A Arria 10 GX FPGA Evaluation Board von Intel (Abbildung 5). Mit dieser Karte können Designer Arria 10-basierte PCI Express (PCIe) 3.0-Designs entwickeln und testen; Speicher-Subsysteme bestehend aus DDR4-, DDR3-, QDR IV- und RLDRAM III-Speichern entwickeln und testen; und modulare und skalierbare Designs entwickeln, indem sie die FPGA-Mezzanine-Karten (FMC)-Steckverbinder als Schnittstelle zu einer von Intel-Partnern bereitgestellten FMC-Mezzanine-Karte verwenden.

Abbildung 5: Das FPGA-Entwicklungskit DK-DEV-10AX115S-A Arria 10 GX liefert eine komplette Designumgebung, die die gesamte Hardware und Software enthält, die für die Entwicklung und den Test von PCIe-basierten Designs, Speicher-Subsystemen und Systemen auf der Basis von FMC-Karten erforderlich ist. (Bildquelle: Intel)

Abbildung 5: Das FPGA-Entwicklungskit DK-DEV-10AX115S-A Arria 10 GX liefert eine komplette Designumgebung, die die gesamte Hardware und Software enthält, die für die Entwicklung und den Test von PCIe-basierten Designs, Speicher-Subsystemen und Systemen auf der Basis von FMC-Karten erforderlich ist. (Bildquelle: Intel)

Die Stratix 10-FPGAs und SoC-FPGAs von Intel sind mit der Intel Hyperflex-FPGA-Architektur ausgestattet. Die FPGAs dieser Bausteinreihe erfüllen die Anforderungen von Systemen mit hohem Durchsatz mit bis zu 10 TFLOPS Gleitkomma-Leistung und Transceiver-Unterstützung von 28,3 Gbits/s (GX) bis 57,8 Gbits/s, letztere in bis zu 144 Transceiver-Lanes, um die Bandbreitenanforderungen von 5G-Kommunikation, Cloud Computing, Netzwerkvirtualisierung und optischen Transportnetzwerken zu erfüllen. Eine Variante umfasst eine PCIe Gen4-Schnittstelle mit einer Konfiguration von bis zu x16 bei 16 Giga-Transfers pro Sekunde (GT/s) und einen neuen Speicher-Controller zur Unterstützung eines ausgewählten persistenten Intel Optane DC-Speichers.

Die Entwicklung mit der Stratix 10-Reihe wird von Intels DK-DEV-1SGX-L-A Stratix 10 GX FPGA-Evaluierungsboard unterstützt (Abbildung 6). Mit dieser Karte können Konstrukteure Stratix 10-basierte PCI Express (PCIe) 3.0-Designs entwickeln und testen; Speicher-Subsysteme bestehend aus DDR4-, DDR3-, QDR IV- und RLDRAM III-Speichern entwickeln und testen; und modulare und skalierbare Designs entwickeln, indem sie die FPGA Mezzanine Card (FMC)-Steckverbinder als Schnittstelle zu einer FMC Mezzanine Card verwenden, die wiederum von Intel-Partnern bereitgestellt wird.

Abbildung 6: Das FPGA-Evaluierungsboard DK-DEV-1SGX-L-A Stratix 10 GX liefert eine komplette Designumgebung, die alle Hardware und Software enthält, die für die Entwicklung und den Test von PCIe-basierten Designs, Speicher-Subsystemen und Systemen auf der Basis von FMC-Karten erforderlich ist. (Bildquelle: Intel)

Abbildung 6: Das FPGA-Evaluierungsboard DK-DEV-1SGX-L-A Stratix 10 GX liefert eine komplette Designumgebung, die alle Hardware und Software enthält, die für die Entwicklung und den Test von PCIe-basierten Designs, Speicher-Subsystemen und Systemen auf der Basis von FMC-Karten erforderlich ist. (Bildquelle: Intel)

Design und Entwicklung mit Intels FPGAs und SoCs FPGAs

In Teil 1 dieser Serie über FPGAs haben wir festgestellt, dass die traditionelle Art und Weise, diese Bausteine zu entwerfen, darin besteht, dass die Ingenieure eine Hardware-Beschreibungssprache (HDL) wie Verilog oder VHDL verwenden, um die Absicht des Designs auf einer Abstraktionsebene zu erfassen, die als Register-Transfer-Ebene (RTL) bekannt ist. Diese RTL-Beschreibungen können zunächst simuliert werden, um zu verifizieren, dass sie wie erforderlich funktionieren. Danach werden sie an ein Synthesewerkzeug weitergeleitet, das die Konfigurationsdatei generiert, die zur Konfiguration (Programmierung) des FPGAs verwendet wird.

Der nächste Schritt in der Abstraktion besteht darin, die Absicht des Entwurfs mit einer Programmiersprache wie C/C++ oder einer speziellen Implementierung wie SystemC zu erfassen, bei der es sich um eine Reihe von C++-Klassen und Makros handelt, die eine ereignisgesteuerte Simulationsschnittstelle bereitstellen. Diese erleichtern die Simulation von gleichzeitigen Prozessen, die jeweils mit einfacher C++-Syntax beschrieben werden. Solche Beschreibungen können analysiert und profiliert werden, indem sie wie normale Programme ausgeführt werden. Danach werden sie an eine High-Level-Synthese-Engine (HLS) weitergeleitet, die RTL ausgibt, das in die reguläre Synthese-Engine eingespeist wird.

Auf einer konzeptionell höheren Abstraktionsebene befindet sich Open CL (Open Computing Language), ein Framework zum Schreiben von Programmen, die auf heterogenen Plattformen ausgeführt werden. Zusätzlich zu FPGAs umfassen diese Plattformen Zentraleinheiten (CPUs), Grafikverarbeitungseinheiten (GPUs), digitale Signalprozessoren (DSPs) und andere Prozessoren oder Hardwarebeschleuniger. OpenCL spezifiziert Programmiersprachen (basierend auf C99 und C++11) für die Programmierung dieser Geräte sowie Programmierschnittstellen (APIs) für die Steuerung der Plattform und die Ausführung von Programmen auf den Rechengeräten.

Im Fall von Intel-FPGAs und SoC-FPGAs entwickeln Anwender Designs für alle Produktfamilien mit Intel Quartus Prime Design Software. Diese Software ist in drei Versionen erhältlich: Quartus Prime Pro Edition, Quartus Prime Standard Edition und Quartus Prime Lite Edition. Die Pro- und Standard-Editionen erfordern kostenpflichtige Lizenzen, während die Lite-Edition kostenlos heruntergeladen werden kann.

Die Pro Edition ist optimiert, um die erweiterten Funktionen in den FPGAs und SoC-FPGAs der nächsten Generation mit den Bausteinfamilien Agilex, Stratix 10, Arria 10 und Cyclone 10 GX zu unterstützen; die Standard Edition bietet neben der Cyclone 10 LP-Bausteinfamilie auch umfangreiche Unterstützung für frühere Bausteinfamilien; und die Lite Edition, die als kostenloser Download ohne Lizenzdatei verfügbar ist, bietet einen idealen Einstieg in hochvolumige Bausteinfamilien.

Intel bietet eine riesige Auswahl an zusätzlichen Design-Tools und Ressourcen, einschließlich Intel DSP Builder, Intel High Level Synthesis (HLS) Compiler und Intel FPGA SDK für OpenCL.

Nützlich ist auch die Intel-Distribution des OpenVINO-Toolkits, die es Entwicklern ermöglicht, Anwendungen für künstliche Intelligenz (KI), Computer Vision, Audio, Sprache und Sprachanwendungen zu erstellen, die tiefe lernende Rückschlüsse vom Rand bis zur Wolke ermöglichen. Zusätzlich zu den FPGAs unterstützt dieses Toolkit die heterogene Ausführung von Intel-Architektur- und AI-Beschleunigern - CPUs, iGPUs, Intel Movidius Vision Processing Unit (VPU) und Intel Gaussian & Neural Accelerator (GNA) - unter Verwendung einer gemeinsamen API. Dieses Toolkit wird durch das OpenVINO Starter Kit unterstützt, das auf dem Cyclone V GT FPGA basiert.

Fazit

Optimale Verarbeitungsdesignlösungen werden oft durch Kombinationen von Prozessoren und FPGAs, durch FPGAs allein oder durch FPGAs mit harten Prozessorkernen als Teil ihrer Struktur bereitgestellt. Als Technologie haben sich FPGAs im Laufe der Jahre schnell entwickelt und sind in der Lage, viele Designanforderungen in Bezug auf Flexibilität, Verarbeitungsgeschwindigkeit und Leistung zu erfüllen, was sie für ein breites Spektrum von Anwendungen von intelligenten Schnittstellen bis hin zu maschineller Bildverarbeitung und künstlicher Intelligenz sehr nützlich macht.

Das Angebot an programmierbaren Bausteinen von Intel reicht vom niedrigen bis zum extrem hohen Bereich, von traditionellen FPGAs bis hin zu SoC-FPGAs. Wie gezeigt, bieten Intel und andere Dritthersteller für die Erstellung von Designs mit diesen Geräten ein leistungsstarkes Paket von Entwicklungskits und -werkzeugen an, die auf die Bedürfnisse von Hardware- und Softwareentwicklern sowie den Schöpfern von Systemen mit künstlicher Intelligenz und Computer Vision zugeschnitten sind.

Weiterführende Literatur

- Grundlagen der FPGAs: Was sind FPGAs und wofür sind sie erforderlich?

- Grundlagen der FPGAs – Teil 2: Erste Schritte mit den FPGAs von Lattice Semiconductor

- Grundlagen von FPGAs - Teil 3: Erste Schritte mit den FPGAs von Microchip Technology

- Grundlagen von FPGAs - Teil 4: Erste Schritte mit Xilinx FPGAs

- FPGAs 101: Eine Einführung für Anfänger

- mplementierung von Low-Power, High-Performance Edge-Computing unter Verwendung von Efinix' quantenfähigen FPGAs

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.