Analoge Grundlagen - Teil 3: Pipeline-ADCs und wie man sie verwendet

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2020-07-14

Hinweis des Editors: Analog/Digital-Wandler (ADCs) verbinden die analoge mit der digitalen Welt und sind somit eine grundlegende Komponente jedes elektronischen Systems, das eine Verbindung zur realen Welt herstellt. Sie sind auch ein entscheidender Faktor zur Bestimmung der Leistung eines Systems. In dieser Reihe werden die Grundlagen der ADCs, ihre verschiedenen Arten und ihre Anwendung untersucht. Teil 1 behandelt SAR-ADCs; Teil 2 behandelt Delta-Sigma(ΔƩ)-Wandler; und hier werden in Teil 3 die Merkmale, Eigenschaften und Verwendung von Pipeline-ADCs diskutiert. Teil 4 zeigt, wie Delta-Sigma-ADCs extrem rauscharme Ergebnisse erzeugen können. Teil 5 befasst sich mit schwierigen Eingangs-Treiberfragen für SAR-ADCs.

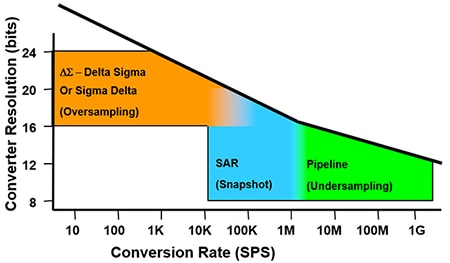

Einige der Anwendungen, die von ADCs bedient werden, sind Basisstationen für Ultrahighspeed-Mehrträger-Mobilfunkinfrastrukturen, Telekommunikation, Beobachtungen der digitalen Vorverzerrung und Backhaul-Empfänger - alle diese Anwendungen erfordern ADCs, die im Bereich von Gigasamples pro Sekunde messen. Teil 1 und Teil 2 dieser Serie über analoge Grundlagen erörtern die ADCs mit sukzessiven Approximationsregistern (SAR) bzw. Delta-Sigma(ΔƩ)-ADCs und deren Anwendungen. Keine der beiden Technologien ist jedoch der Herausforderung gewachsen, Ergebnisse in Gigasamples pro Sekunde (GS/s) zu erzeugen.

Beispielsweise verwendet der SAR-ADC einen „Schnappschuss“-Algorithmus, so dass seine Geschwindigkeit aufgrund seines seriellen Ansatzes auf 10 Megasamples pro Sekunde (MS/s) begrenzt ist. Im Fall des hochauflösenden Oversampling-Algorithmus der ΔƩ-ADCs erfordert dies zusätzliche Zeit für die Erfassung und Mittelung mehrerer Abtastwerte, die 24-Bit-Ausgabedatenraten von bis zu 5 Megahertz (MHz) erzeugen. Die GSPS-Raten liegen weit außerhalb des Abtastfrequenzbereichs der SAR-ADCs und ΔƩ-ADCs.

Die Lösung für diese Ultra-Hochgeschwindigkeits-ADC-Herausforderung ist ein Pipeline-ADC, der mehrere Abtastwerte verarbeitet und trotzdem Daten mit GSPS-Geschwindigkeit an seinen Ausgang sendet.

Dieser Artikel vergleicht kurz ΔƩ-, SAR- und Pipeline-ADCs und erörtert dann die mit der Erzielung von Hochgeschwindigkeits-Wandlerausgängen verbundenen Probleme und warum Pipeline-ADCs eine ausgezeichnete Alternative für diese Hochgeschwindigkeitsanwendungen sind. Anschließend werden zwei Pipeline-ADCs von Texas Instruments vorgestellt - das eine betont die Präzision, das andere die hohe Geschwindigkeit - und es wird gezeigt, wie man sie verwendet.

Was ist ein Pipeline-ADC?

Ein Pipeline-ADC besteht aus mehreren aufeinander folgenden Stufen. Die differenziell strukturierte erste Stufe wertet den Wert des höchstwertigen Bits (MSB) aus und konditioniert dann das Signal und leitet es an die nächste Stufe für eine MSB-1-Wandlung weiter. Jede Stufe führt ihre Operation gleichzeitig mit anderen Stufen durch (Abbildung 1).

Abbildung 1: Die Pipeline-Topologie hat mehrere Stufen, um die Konvertierung eines Bits des Multi-Bit-Konverters zu implementieren, und konditioniert dann das Signal und leitet das Signal an die nächste Stufe weiter. (Bildquelle: Texas Instruments)

Abbildung 1: Die Pipeline-Topologie hat mehrere Stufen, um die Konvertierung eines Bits des Multi-Bit-Konverters zu implementieren, und konditioniert dann das Signal und leitet das Signal an die nächste Stufe weiter. (Bildquelle: Texas Instruments)

In Abbildung 1 sind die Stufen in ihrer Funktion ähnlich und lösen nur ein oder zwei Bits auf. Jede Stufe verfügt über eine Abtast- und Haltefunktion, einen Flash-ADC mit niedriger Auflösung und eine Signalkonditionierungsfunktion. Die erste Stufe erhält die Probe und produziert sofort eine MSB-Entscheidung. Der MSB-Digitalwert geht an das erste Halteglied (Latch 1). Wenn die MSB-Entscheidung eins ist, subtrahiert die Stufe den MSB-Wert der Ladung von der Probe. Dann wendet der Pipeline-Konverter ein 2x Verstärkungsfaktor auf die verbleibende Ladung an. Wenn eine Stufe ihre Operationen abgeschlossen hat, gibt sie die analoge Differenz an die nachfolgenden Stufen weiter. Das Schöne an dem Design mit dem 2-fachen Verstärkungsfaktor ist, dass die Stufen 1 bis n im Wesentlichen die gleichen Schaltungen sind.

Die Anzahl der Stufen entspricht oft der Anzahl der ADC-Bits. Die endgültige Konvertierungsausgabe kombiniert die digitalen Ergebnisse jeder Stufe im Ausgabespeicher. Dieser Konvertierungsprozess führt zu einer Datenlatenz von mehreren Taktzyklen.

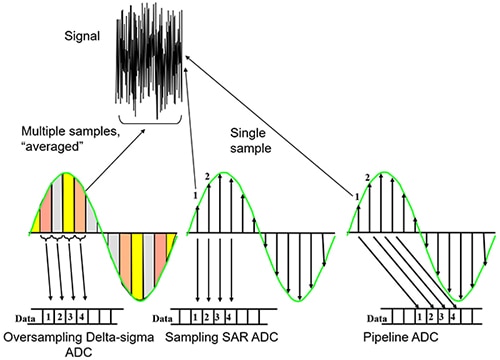

Vergleich der Abtastungen von ΔΣ-, SAR- und Pipeline-ADC

Der ΔΣ-Wandler verwendet einen Oversampling-Algorithmus, um digitale Filter mit endlicher Impulsantwort (FIR) oder unendlicher Impulsantwort (IIR) zu implementieren. Diese Filter erzeugen bei der Erfassung mehrerer Abtastwerte eine Signalausgangslatenz oder -verzögerung, wodurch als positiver Kompromiss eine extrem hohe Auflösung erzielt wird. Infolgedessen ist die Erfassungszeit länger als bei einem SAR- oder Pipeline-Konverter, die beide das Signal bei jeder Konvertierung nur einmal abtasten (Abbildung 2).

Abbildung 2: Der langsame, höchstauflösende ΔƩ-ADC bedient Signale mit niedrigerer Frequenz. Der SAR-ADC mit mittlerer Geschwindigkeit und mittlerer Auflösung dient allgemeinen Anwendungen. Der Highspeed-Pipeline-ADC mit niedrigerer Auflösung passt in führende Hochgeschwindigkeitslösungen. (Bildquelle: DigiKey)

Abbildung 2: Der langsame, höchstauflösende ΔƩ-ADC bedient Signale mit niedrigerer Frequenz. Der SAR-ADC mit mittlerer Geschwindigkeit und mittlerer Auflösung dient allgemeinen Anwendungen. Der Highspeed-Pipeline-ADC mit niedrigerer Auflösung passt in führende Hochgeschwindigkeitslösungen. (Bildquelle: DigiKey)

Der SAR-ADC gibt eine Momentaufnahme des Eingangssignals mit einem definierten Erfassungszeitpunkt wieder. Bei Verwendung von Techniken zur Ladungsumverteilung schließt der SAR schnell eine Null-Latenz-Konvertierung ab. Der Pipeline-Konverter verwendet Unterabtastungstechnologien, um durch den Einsatz von Ladungsumverteilungstechniken Highspeed-Konvertierungen zu erreichen und das Erscheinen der Ergebnisse auf der Ausgabe zu verzögern. Dieser Konvertierungsalgorithmus erzeugt eine Datenlatenz.

Die Latenzzeit im Vergleich zur Konvertierungsgeschwindigkeit unterscheidet sich zwischen dem SAR-, Pipeline- und ΔƩ-Wandler (Abbildung 3).

Abbildung 3: Der ΔƩ-Oversampling- und -Mittelungsalgorithmus erzeugt eine Verzögerung beim Erscheinen des endgültigen Ausgabedatenwortes. Da die Ausgabe des SAR-ADC vor der nächsten Probenerfassung erscheint, ist die Latenzzeit des SAR-ADC gleich Null. Die Datenergebnisverzögerung des Pipeline-Konverters erzeugt eine Latenzzeit ungleich Null. (Bildquelle: DigiKey)

Abbildung 3: Der ΔƩ-Oversampling- und -Mittelungsalgorithmus erzeugt eine Verzögerung beim Erscheinen des endgültigen Ausgabedatenwortes. Da die Ausgabe des SAR-ADC vor der nächsten Probenerfassung erscheint, ist die Latenzzeit des SAR-ADC gleich Null. Die Datenergebnisverzögerung des Pipeline-Konverters erzeugt eine Latenzzeit ungleich Null. (Bildquelle: DigiKey)

In Abbildung 3 mittelt der ΔƩ-Wandler mehrere Proben für jedes Konvertierungsergebnis. Der Mittelwertbildungsfilter von ΔƩ ist normalerweise ein digitaler FIR- oder IIR-Filter. Diese Multi-Sampling-Mittelung erhöht die Gesamtumwandlungszeit. Es sind jedoch hohe Auflösungen möglich, wodurch eine Abhängigkeit zwischen Durchsatzzeit und Genauigkeit entsteht.

Die Konvertierungszeit des SAR-Konverters umfasst die Erfassungszeit des Eingangssignals und die Konvertierungszeit. Die Erfassungszeit ermöglicht es, dass sich das Eingangssignal beruhigt, bevor der eigentliche Moment der Signalerfassung eintritt. Die Durchsatzzeit ist eine Kombination aus interner Ladungsumverteilung und aufeinanderfolgenden seriellen Datenausgabesignalen, beginnend mit dem MSB-Wert.

Bei einem Pipeline-ADC initiiert der Anwender mit der steigenden (oder fallenden) Flanke des externen Eingangstaktes eine Abtasterfassung. Die erfasste Ladung für diese Probe geht in eine zweite Stufe, während der Wandler das Ladungsäquivalent eines anderen Eingangssignals erfasst und die zweite Stufe den MSB-Wert ermittelt. Bei dem folgenden externen Takt geht das zweite erfasste Signal an die zweite Stufe, während das erste Signal an die dritte Stufe geht. Während dieses Taktzyklus erfolgt die Bestimmung des MSB-1 des ersten erfassten Signals und des MSB des zweiten erfassten Signals. Dieser Prozess setzt sich mit jedem erfassten Signal fort. Wenn ein Eingangssignal eine vollständige digitale Ausgangsdarstellung hat, stellt die Ausgangsstufe des Wandlers eine parallele Darstellung des Eingangssignals dar.

Das Ergebnis dieser Architektur ist, dass Pipeline-ADCs für Abtastraten von einigen wenigen Megasamples pro Sekunde bis über 1 GS/s beliebt sind. Die Auflösungen reichen von 8 Bit bei schnelleren Abtastraten bis zu 16 Bit bei niedrigeren Raten. Diese Auflösungen und Abtastraten decken ein breites Spektrum von Anwendungen ab, darunter CCD-Bildgebung (charge coupled device), medizinische Ultraschall-Bildgebung, digitale Empfänger, Basisstationen, digitale Vorverzerrung und digitales Video. Bei einigen dieser Anwendungen liegt der Schwerpunkt sowohl auf Präzision als auch auf Geschwindigkeit.

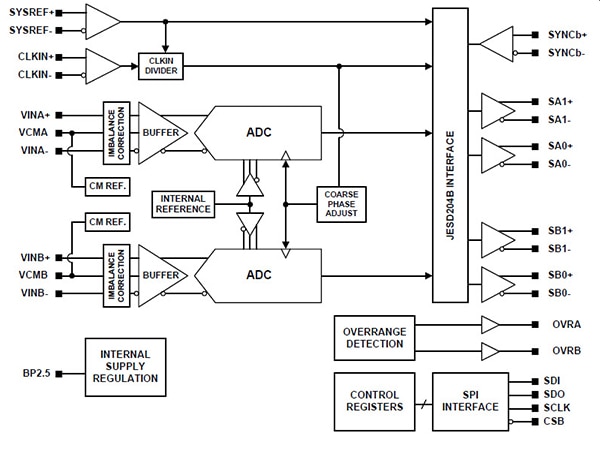

Präzise Pipeline-ADCs

Ein gutes Beispiel für einen Präzisions-Pipeline-ADC ist der ADC16DX370 von Texas Instruments, ein Zweikanal-Pipeline-ADC mit 16 Bit und 370 MS/s, gefolgt von einer JESD204B-Backend-Schnittstelle mit 7,4 Gigabit pro Sekunde (Gbit/s). Bei einem 150-MHz-Eingangssignal betragen das Signal-Rausch-Verhältnis (SNR), der störungsfreie Dynamikbereich (SFDR) und die spektrale Rauschdichte (NSD) des ADC16DX370 69,6 Dezibel bei Vollaussteuerung (dBFS), 88 dBFS bzw. -152,3 dBFS/Hertz.

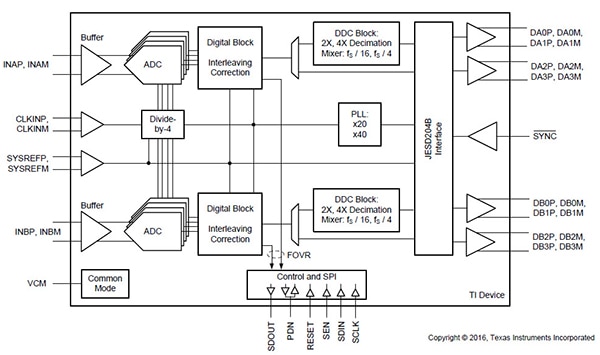

Jeder ADC verfügt über einen Eingangspuffer und eine Unsymmetriekorrekturschaltung sowie über die notwendigen Referenzspannungen mit internen Treibern. Der integrierte Eingangspuffer eliminiert das interne Ladungsrauschen des geschalteten Abtastkondensators und das Ladungs-Kickback-Rauschen. Dieser Puffer entlastet den Treiberverstärker, den Anti-Aliasing-Filter und die Anforderungen an die Impedanzanpassung (Abbildung 4).

Abbildung 4: Der leistungsstarke ADC16DX370 für 370 MS/s ist ein Dual-Pipeline-ADC mit einer internen Referenz. Er wandelt analoge Signale in digitale 16-Bit-Wörter um. (Bildquelle: Texas Instruments)

Abbildung 4: Der leistungsstarke ADC16DX370 für 370 MS/s ist ein Dual-Pipeline-ADC mit einer internen Referenz. Er wandelt analoge Signale in digitale 16-Bit-Wörter um. (Bildquelle: Texas Instruments)

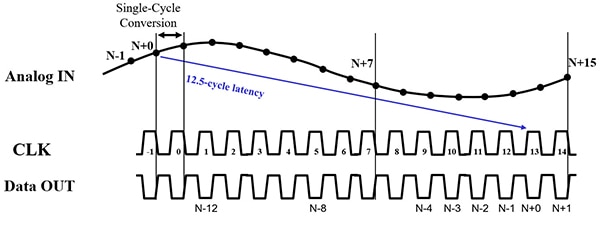

Der ADC16DX370 leitet den Abtasttakt aus dem CLKIN-Eingang mit einem rauscharmen Empfänger und Taktteiler ab. Ein Eingangstaktteiler verteilt ein hochfrequentes Taktsignal im gesamten System und teilt lokal am ADC-Baustein herunter, um eine Kopplung von Signalen mit gemeinsamen Zwischenfrequenzen (ZFs) in andere Teile des Systems zu vermeiden. Die Kernlatenz des ADC beträgt 12,5 Taktzyklen (Abbildung 5).

Abbildung 5: Das Timing-Diagramm zeigt, dass die Latenzzeit des ADC-Kerns 12,5 Taktzyklen beträgt. (Bildquelle: DigiKey)

Abbildung 5: Das Timing-Diagramm zeigt, dass die Latenzzeit des ADC-Kerns 12,5 Taktzyklen beträgt. (Bildquelle: DigiKey)

Die Abtastung erfolgt an der steigenden Flanke des Differenzsignals (CLKIN+) - (CLKIN-). Als minimaler Kernwert steht der digitale Ausgabecode nach 12,5 Taktzyklen Datenlatenz zur Verfügung. Die CLKIN-Eingangsfrequenzteilerfaktoren sind 1, 2, 4 oder 8.

Der ADC16DX370 verfügt über differentielle Takteingangspins. Die interne Terminierung gegen Gleichstrom jedes Pins ist ein 50-Ohm-Widerstand (Ω) für eine 100 Ω gesamte interne differentielle Terminierung. Die Takteingangspins erfordern eine externe AC-Kopplung.

Das Dual-Pipeline-ADC-Leiterplattendesign ist für das Erreichen der vollen Leistung entscheidend. Mindestens sechs Schichten sind erforderlich, um alle Signale adäquat in den Baustein hinein und aus dem Baustein heraus zu leiten. Signalführungsschichten benötigen angrenzende feste Masseebenen zur Steuerung von Signalrückwegen, um Schleifenbereiche zu minimieren, und das Routing von Mikroleitungen und Streifenleitungen muss sorgfältig durchgeführt werden, um Impedanzen zu steuern. Der Einsatz von Versorgungsebenen und angrenzenden festen Masseebenen steuert die Rücklaufwege der Versorgung. Auch die Minimierung des Abstands zwischen Versorgungs- und Masseebenen erhöht die verteilte Entkopplung und verbessert die Leistung.

Die Zielanwendungen für den ADC16DX370 sind Empfänger mit hoher ZF-Abtastung, Multi-Carrier-Basisstationsempfänger und Multi-Mode- und Multi-Band-Empfänger, die die höhere Auflösung und die 370 MS/s Umwandlungsgeschwindigkeit ergänzen. Dieser 16-Bit-Pipeline-ADC bietet die erforderliche SNR-Leistung (69,6 dBFS) zur Unterscheidung kleiner Signale vom Hintergrundrauschen z.B. in einem HF-Heterodyn-Empfänger-Subsystem.

Um Entwicklern die Evaluierung des ADC16DX370 zu erleichtern, wird der ADC von der Evaluierungsplatine ADC16DX370EVM mit zugehöriger Software High-Speed Data Converter (HSDC) Pro unterstützt. Das EVM wird mit einem Mini-USB-Kabel zum Anschluss an einen PC geliefert. TI bietet auch das Referenzdesign-Board TSW16DX370EVM an, das zur Evaluierung einer Empfänger-ZF-Subsystemlösung mit über 100 MHz nutzbarer Bandbreite verwendet werden kann.

Highspeed-Pipeline ADCs

Wenn sowohl hohe Geschwindigkeit als auch ein großer Dynamikbereich Priorität haben, können Entwickler auf den ADC ADS54J20 von Texas Instruments zurückgreifen, einen 12-Bit-Zweikanal-ADC mit 1 GS/s. Das Design dieses ADC bietet einen hohen SNR von 67,8 dBFS bei einem Rauschabstand von -157 dBFS/Hz. Dieser ADC eignet sich perfekt für Anwendungen, die den höchsten Dynamikbereich über eine große Momentanbandbreite anstreben (Abbildung 6).

Abbildung 6: Der Dual-Pipeline-ADC ADS54J20 bietet eine Interleaving-Korrektur, um einen Rauschpegel von -157 dBFS/Hz und digitale Filteroptionen zur Dezimierung zu erreichen. (Bildquelle: Texas Instruments)

Abbildung 6: Der Dual-Pipeline-ADC ADS54J20 bietet eine Interleaving-Korrektur, um einen Rauschpegel von -157 dBFS/Hz und digitale Filteroptionen zur Dezimierung zu erreichen. (Bildquelle: Texas Instruments)

In Abbildung 6 werden die Verschachtelungs- und Dithering-Algorithmen des ADS54J20 verwendet, um ein sauberes Spektrum mit einem hohen SFDR zu erzielen. Der Baustein verfügt außerdem über verschiedene programmierbare Dezimationsfilteroptionen für Systeme, die ein höheres SNR und SFDR über einen großen Frequenzbereich benötigen.

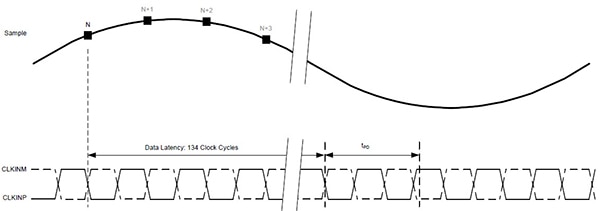

Der Bandpass-Dezimationsfilter verfügt über einen digitalen Mischer und drei verkettete FIR-Filter, um eine Latenzzeit von etwa 134 Ausgangstaktzyklen zu erzeugen, sowie über Logikgatter und eine Ausbreitungsverzögerung des Ausgangspuffers, die 4 Nanosekunden (ns) beträgt (Abbildung 7).

Abbildung 7: Das Timing-Diagramm zeigt eine ADC-Latenz von 134 Taktzyklen plus Logikgatter und Ausbreitungsverzögerung des Ausgangspuffers (tPD). (Bildquelle: Texas Instruments)

Abbildung 7: Das Timing-Diagramm zeigt eine ADC-Latenz von 134 Taktzyklen plus Logikgatter und Ausbreitungsverzögerung des Ausgangspuffers (tPD). (Bildquelle: Texas Instruments)

Der Digitalblock, die Interleaving-Engine und der Dezimationsfilter (wiederum Abbildung 6) tragen in Kombination mit der schnellen Abtastung mit einer Taktfrequenz von 1 Gigahertz (GHz) zur Latenz des Konverters bei.

Einige der Zielanwendungen für den ADS54J20 sind Radar- und Antennenarrays, drahtlose Breitbanddienste, ein Kabelmodem-Abschlusssystem (CMTS) und DOCSIS 3.1-Empfänger.

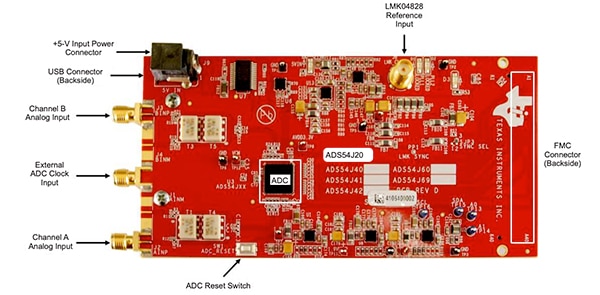

Der ADS54J20 wird auch von einem Evaluierungsboard unterstützt, in diesem Fall dem ADS54J20EVM (Abbildung 8).

Abbildung 8: Der Highspeed-ADC ADS54J20 wird vom Evaluierungsboard ADS54J20EVM unterstützt, das mit einem Mini-USB-Kabel und einem Stromversorgungskabel geliefert wird. (Bildquelle: Texas Instruments).

Abbildung 8: Der Highspeed-ADC ADS54J20 wird vom Evaluierungsboard ADS54J20EVM unterstützt, das mit einem Mini-USB-Kabel und einem Stromversorgungskabel geliefert wird. (Bildquelle: Texas Instruments).

Der ADS54J20EVM wird auch in Verbindung mit der Software HSDC Pro verwendet und wird mit einem Mini-USB-Kabel zum Anschluss an einen PC sowie einem Stromversorgungskabel geliefert.

Fazit

Während SAR- und ΔƩ-ADCs ihren Platz haben, ist die Lösung für die Ultra-Highspeed-ADC-Herausforderung ein Pipeline-ADC, der mehrere Abtastwerte verarbeitet und dabei immer noch Daten mit Geschwindigkeiten von Hunderten von Kilosamples pro Sekunde bis hin zu Gigasamples pro Sekunde an seinen Ausgang sendet. Dennoch legen nicht alle Pipeline-ADCs den Schwerpunkt allein auf Geschwindigkeit. Wie gezeigt, kann auch eine höhere Präzision erreicht werden.

Unabhängig vom Schwerpunkt sind Pipeline-ADCs eine ausgezeichnete Option für Highspeed-Mobilfunk-Basisstationen, ultraschnelle Mobilfunk-Basisstationen für die Multi-Carrier-Infrastruktur, Telekommunikation, digitale Vorverzerrungsbeobachtungen, Backhaul-Empfänger und viele andere Anwendungen, die eine Highspeed-Umwandlung erfordern.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.