Implementierung leistungsfähiger programmierbarer Taktgeneratoren für Rechenzentren und industrielle Systeme

Ein genaues Timing zur Unterstützung der Kommunikation über Ethernet und PCIe (Peripheral Component Interconnect express) ist wichtig und kann bei der Entwicklung von Servern, Speichersystemen und Netzwerken oder eingebetteten Industriesystemen eine Herausforderung darstellen. Es geht nicht nur darum, einen Ethernet- oder PCIe-Bus hinzuzufügen. Ein typisches Design kann mehrere Busse umfassen, die alle eine genaue Timing-Unterstützung mit einem Minimum an Jitter benötigen. Ein typisches System erfordert eine Mischung von Kommunikationsbussen, die mit verschiedenen Frequenzen bis zu 650 Megahertz (MHz) arbeiten.

Es werden Lösungen benötigt, die so wenig Platz wie möglich auf der Leiterplatte einnehmen. Darüber hinaus unterscheiden sich die Timing-Anforderungen von Ethernet und PCIe, was die Herausforderung für das Design erhöht. Um diese Anforderungen zu erfüllen, können kompakte programmierbare Taktgenerator-ICs verwendet werden, die gleichzeitig bis zu 12 Referenztakte für Ethernet- und PCIe-Busse liefern können.

Dieser Blog gibt einen kurzen Überblick über die Timing-Anforderungen von Ethernet- und PCIe-Bussen und stellt dann kompakte programmierbare Taktgeneratorlösungen von Renesas vor, die gleichzeitig die Anforderungen mehrerer PCIe- und Ethernet-Busse erfüllen. Außerdem werden Evaluierungsboards vorgestellt, die die Entwicklung von Timing-Schaltungen in Servern, Speichersystemen, Netzwerken oder eingebetteten Industriesystemen beschleunigen.

Kontrolle von Jitter und Minimierung von EMI

PCIe und Ethernet werden für unterschiedliche Zwecke verwendet. Zu den PCIe-Anwendungen gehören die Chip-zu-Chip-Kommunikation auf einer PC-Platine und Verbindungen zu Erweiterungskarten, während Ethernet für lokale Netzwerke (LANs), Speichernetzwerke (SANs) und ähnliche Anwendungen verwendet wird. Die verschiedenen Betriebsumgebungen stellen unterschiedliche Anforderungen an die Schaltungen für das Timing.

Die Jitter-Dämpfung ist in Ethernet-Netzen von entscheidender Bedeutung. Bei Highspeed-Ethernet mit bis zu 650 Megahertz (MHz) muss beispielsweise der Effektivwert (RMS) des Phasenjitters auf maximal 150 Femtosekunden (fs) begrenzt werden, um die Signalintegrität, geringere Laufzeitverzögerungen und ein vorhersehbares Verhalten zu gewährleisten.

Neben der Kontrolle des Jitters profitieren PCIe-Busse von der Spreizspektrum-Modulation, die die Jitter-Energie über einen größeren Frequenzbereich verteilt und so elektromagnetische Störungen (EMI) minimiert. Die Unterdrückung der EMI bedeutet, dass weniger Abschirmungen auf den Leiterplatten erforderlich sind, was die Systemkosten senkt und die Systemintegration beschleunigt. Mit den VersaClock-Generatoren von Renesas können Sie den Umfang der Spreizspektrummodulation steuern, um die für bestimmte Anwendungen erforderlichen Kompromisse zwischen Kosten und Leistung zu optimieren.

Mehr leisten auf weniger Raum

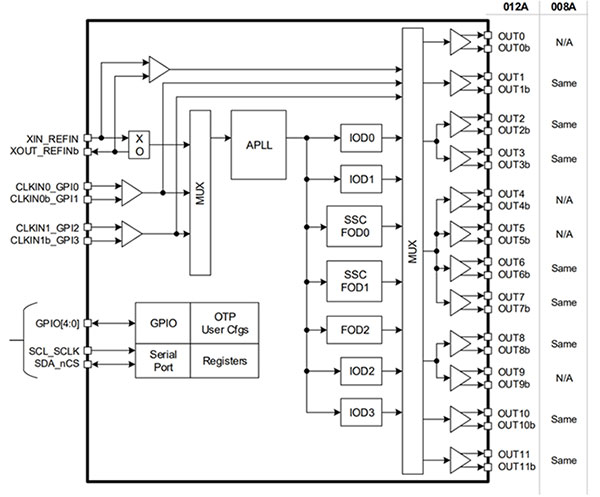

Eine integrierte Timing-Lösung auf der Basis von VersaClock-Generatoren von Renesas ermöglicht es Ihnen, mehr auf weniger Platz auf der Leiterplatte zu erreichen. Sie sind mit 8 oder 12 unabhängigen Taktgebern erhältlich und verfügen über die folgenden Merkmale (Abbildung 1):

- Phasenjitter von 169 fs effektiv (10 Kilohertz (kHz) - 20 MHz, 156,25 MHz)

- PCIe-Gen6-Takt (CC, Common Clock) 27 fs effektiv

- Unterstützung für PCIe-Betrieb mit SRIS (Separate Reference Independent Spread) und SRNS (Separate Reference No Spread)

- 1 kHz bis 650 MHz LVDS-Ausgänge (Low Voltage Differential Signaling) und LP-HCSL-Ausgänge (Low-Power, High-Speed Current Steering Logic)

Abbildung 1: Es gibt programmierbare VersaClock-Taktgeneratoren, die bis zu acht Takte (Spalte „008A“ rechts) oder bis zu 12 Takte (Spalte „012A“) unterstützen. (Bildquelle: Renesas)

Abbildung 1: Es gibt programmierbare VersaClock-Taktgeneratoren, die bis zu acht Takte (Spalte „008A“ rechts) oder bis zu 12 Takte (Spalte „012A“) unterstützen. (Bildquelle: Renesas)

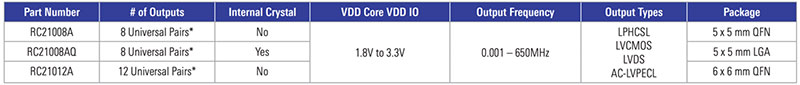

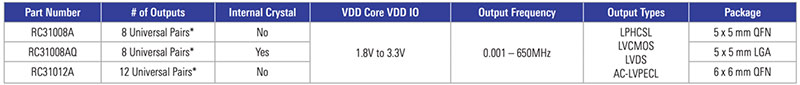

Ein herkömmlicher Ansatz zum Aufbau einer Timing-Lösung mit 5 unabhängigen Taktgebern erfordert einen gemeinsamen Quarzoszillator-Schaltkreis, der etwa 3 x 3 Millimeter (mm) Platz auf der Leiterplatte einnimmt, sowie vier Unteroszillatoren, die jeweils etwa 5 x 3 mm groß sind. Oder Sie können einen einzelnen VersaClock-IC wie den RC21008A verwenden, der nur 5 x 5 mm groß ist. Und derselbe IC kann bis zu acht Taktausgänge unterstützen, was den Platz auf der Leiterplatte, die Anzahl der Komponenten und die Kosten weiter reduziert. Die wichtigsten Merkmale des RC21008A werden zusammen mit zwei anderen ICs aus der Familie VersaClock 7 gezeigt: dem RC21008AQ und dem RC21012A (Tabelle 1).

Tabelle 1: Die wichtigsten Merkmale der 3 Taktgeneratoren der Familie VersaClock 7. Ein „*“ bedeutet, dass die Ausgänge als differenziell oder LVCMOS konfigurierbar sind. (Tabellenquelle: Renesas)

Tabelle 1: Die wichtigsten Merkmale der 3 Taktgeneratoren der Familie VersaClock 7. Ein „*“ bedeutet, dass die Ausgänge als differenziell oder LVCMOS konfigurierbar sind. (Tabellenquelle: Renesas)

Abschwächen von Jitter

Die programmierbaren Jitter-Dämpfungsglieder RC31008A, RC31008AQ und RC31012A verfügen über Netzwerksynchronisationsfunktionen, einschließlich JEDEC JESD204B/C für die Unterstützung der Wandlersynchronisation an unsymmetrischen oder differentiellen Ausgängen mit AC- oder DC-Kopplung sowie Unterstützung für synchrones Ethernet (SyncE) für netzwerkbasierte Synchronisation. Wie die VersaClock-Taktgenerator-ICs sind auch diese Jitter-Dämpfungsglieder mit 8 oder 12 Ausgängen erhältlich, was die Größe und die Kosten der Lösung reduziert (Tabelle 2).

Tabelle 2: Jitter-Dämpfungsglieder der VersaClock 7-Familie. Ein „*“ bezeichnet die Anzahl der Ausgänge, die als differenziell oder LVCMOS konfigurierbar sind. (Tabellendaten: Renesas)

Tabelle 2: Jitter-Dämpfungsglieder der VersaClock 7-Familie. Ein „*“ bezeichnet die Anzahl der Ausgänge, die als differenziell oder LVCMOS konfigurierbar sind. (Tabellendaten: Renesas)

Evaluierungsboards

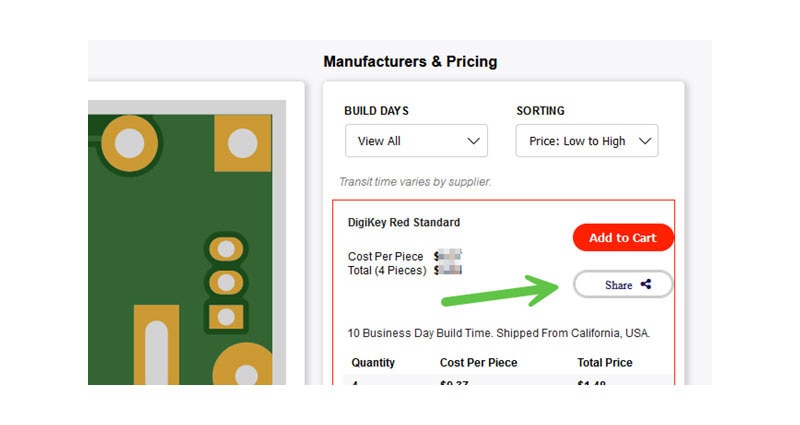

Um Entwicklungsaktivitäten zu beschleunigen, bietet Renesas eine Reihe von Evaluierungsboards (EVBs) an, darunter das RC21008-EVB (Abbildung 2) und das RC21012-EVB für Taktgeneratoren mit 8 bzw. 12 Ausgängen sowie die Evaluierungsboards RC31008-EVB und RC31012-EVB, die für Jitter-Dämpfungsglieder mit 8 bzw. 12 Ausgängen verwendet werden können. Diese EVBs unterstützen die Takterzeugung im Synthesizermodus für PCIe-Konformität und Spreizspektrum-Leistung und können auch den Jitter-Dämpfungsmodus unterstützen. Sie unterstützen Frequenzbereiche des Referenzeingangs von 1 kHz bis 650 MHz im Differenzmodus und von 1 kHz bis 200 MHz im referenzbezogenen Modus. Sie zeichnen sich durch eine typische Verlustleistung von unter 1 Watt und folgende Jitter-Spezifikationen aus:

- 150 fs effektiver Phasenjitter (12 kHz - 20 MHz, ganzzahlig)

- 200 fs effektiver Phasenjitter (12 kHz - 20 MHz, teilzahlig)

Abbildung 2: Evaluierungsboards wie das RC21008-EVB für die Serie VersaClock 7 unterstützen die Entwicklung von Lösungen mit acht Ausgängen. (Bildquelle: Renesas)

Abbildung 2: Evaluierungsboards wie das RC21008-EVB für die Serie VersaClock 7 unterstützen die Entwicklung von Lösungen mit acht Ausgängen. (Bildquelle: Renesas)

Fazit

Wie gezeigt, lassen sich mit den VersaClock-Taktgeneratoren und Jitter-Dämpfungsgliedern von Renesas leistungsstarke, kompakte und kostengünstige Timing-Lösungen für PCIe- und Ethernet-Busse in einer Reihe von Datenverarbeitungs- und Industrieanwendungen entwickeln. Um den Einstieg zu erleichtern, stehen Evaluierungsboards zur Verfügung, die den Entwicklungsprozess beschleunigen und die Markteinführungszeit verkürzen.

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum