I/O-Spannungsstandards und ihre Rolle bei der sicheren Kommunikation zwischen Mikrocontrollern

Stellen Sie sich vor, Sie versuchen, mit einem Ausländer in Ihrer Muttersprache zu kommunizieren (Abbildung 1), und stellen fest, dass er Sie nicht nur nicht versteht, sondern dass Ihr „Ja“ in seiner Sprache eigentlich „Nein“ bedeutet. Genau das passiert, wenn zwei integrierte Schaltungen (ICs) mit inkompatiblen I/O-Standards versuchen, miteinander zu kommunizieren. Das Ergebnis ist bestenfalls Verwirrung und schlimmstenfalls ein Hardwareschaden.

Abbildung 1: KI-generiertes Bild, das die Verwirrung bei der Verwendung verschiedener IO-Standards symbolisiert. (Quelle: KI-generiert)

Abbildung 1: KI-generiertes Bild, das die Verwirrung bei der Verwendung verschiedener IO-Standards symbolisiert. (Quelle: KI-generiert)

Mikrocontroller arbeiten in binärer Logik mit 0 und 1. Es gibt Spannungsbereiche, die diesen Logikpegeln entsprechen. Ein Mikrocontroller kann beispielsweise eine logische 0 als alles lesen, was niedriger als 0,3 V ist, und eine 1 als alles, was größer als 2,7 V und maximal 3,3 V ist. Der andere Mikrocontroller kann jedoch eine 1 als alles lesen, was bei 1,2 V beginnt und maximal 1,8 V ist. Wenn der erste Mikrocontroller ein 3,3V-Signal an den zweiten sendet (Abbildung 2), könnte dies die Spannungstoleranz des empfangenden Geräts überschreiten und möglicherweise dauerhafte Schäden verursachen.

Abbildung 2: Darstellung der Kommunikation zweier ICs mit inkompatiblen IO-Standards. (Quelle: KI-generiert)

Abbildung 2: Darstellung der Kommunikation zweier ICs mit inkompatiblen IO-Standards. (Quelle: KI-generiert)

Aus diesem Grund ist das Verständnis der I/O-Spannungskompatibilität beim Entwurf eingebetteter Systeme von entscheidender Bedeutung. Ohne ordnungsgemäße Pegelwandlung oder Spannungsumsetzung kann selbst eine einfache Verbindung zwischen zwei Chips zu unvorhersehbarem Verhalten oder Hardwareausfällen führen.

Die Rolle von I/O-Spannungsstandards

I/O-Spannungsstandards definieren die zulässigen Spannungspegel für digitale Logiksignale. Sie geben an, was ein logischer High-Pegel (1) oder Low-Pegel (0) ist. Diese Normen gewährleisten, dass die Komponenten Signale richtig interpretieren und angemessen reagieren können. Ohne eine gemeinsam vereinbarte Norm für diese Pegel können Komponenten Signale falsch lesen oder nicht miteinander kommunizieren.

In den Normen definierte Terminologien:

- VIH (High-Eingangspegel): Minimale Spannung, die als logisch High (1) erkannt wird.

- VIL (Low-Eingangspegel): Maximale Spannung, die als logisch Low (0) erkannt wird.

- VOH (High-Ausgangspegel): Minimale Spannungsausgabe für ein logisches High.

- VOL (Low-Ausgangspegel): Maximale Spannungsausgabe für ein logisches Low.

Für eine erfolgreiche Kommunikation müssen die Ausgangspegel einer Komponente innerhalb des zulässigen Eingangsbereichs der empfangenden Komponente liegen.

Referenzbezogene IO-Standards

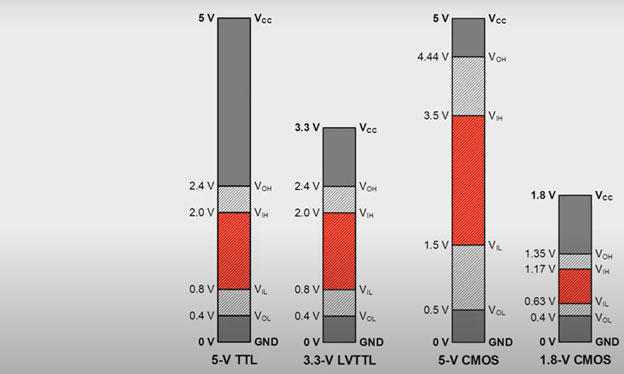

Referenzbezogene IO-Standards (SIO) (Abbildung 3) gehören zu den beliebtesten I/O-Normen. Sie verwenden eine einzige Leitung, die zur Signalübertragung auf eine gemeinsame Masse bezogen ist. Wenn es um Anwendungen mit niedriger Geschwindigkeit und geringer Komplexität geht, sind SIOs eine kostengünstige und einfachere Alternative im Vergleich zu Differenzsignalstandards, die zwei komplementäre Signale verwenden.

LVCMOS (Low Voltage Complementary Metal-Oxide Semiconductor) ist ein gängiger referenzbezogener Standard, der in einigen Zusammenhängen auch als LVMOS bezeichnet wird. LVCMOS arbeitet typischerweise mit 1,8 V, 2,4 V oder 3,3 V und definiert spezifische Schwellenwerte für logische High- und Low-Pegel. Die Einfachheit der SIO-Standards hat ihren Preis: SIOs wie LVCMOS sind anfällig für Rauschen und Signalverschlechterung über lange Strecken oder bei hohen Frequenzen. Die Sicherstellung einer ordnungsgemäßen Spannungskompatibilität unter Verwendung von Pegelwandlern ist von entscheidender Bedeutung, wenn LVCMOS-Bauteile mit Komponenten verbunden werden, die in unterschiedlichen Spannungsbereichen arbeiten.

Abbildung 3: Spannungspegel verschiedener IO-Standards. (Quelle: Texas Instruments)

Abbildung 3: Spannungspegel verschiedener IO-Standards. (Quelle: Texas Instruments)

Herausforderungen bei I/O-Schnittstellen

1. Spannungsfehlanpassung

Das häufigste Problem bei der Kopplung von Komponenten, die mit unterschiedlichen Spannungsniveaus arbeiten, ist die fehlende Spannungsanpassung. So kann beispielsweise der Anschluss eines 3,3V-Ausgangs an einen 1,8V-Eingang ohne Pegelwandlung die Komponente mit der niedrigeren Spannung beschädigen (Abbildung 2).

Um dies abzumildern, muss sichergestellt werden, dass der High-Eingangspegel (VIH) und der Low-Eingangspegel (VIL) des einen IC mit dem High-Ausgangspegel (VOH) und dem Low-Ausgangspegel (VOL) des anderen IC übereinstimmen.

2. Signalintegrität

Bei hohen Geschwindigkeiten können Reflektionen, Klingeln und Übersprechen die Signale stören. Eine ordnungsgemäße Terminierung, Impedanzanpassung und Leiterbahnführung sind unerlässlich, um saubere Signalübergänge zu gewährleisten.

3. Stromversorgungsdomänen

In Systemen mit mehreren Spannungsschienen muss darauf geachtet werden, dass die Signale zwischen den Domänen isoliert oder übersetzt werden. Pegelwandler, Spannungsteiler oder Open-Drain-Konfigurationen mit Pull-up-Widerständen sind gängige Lösungen.

Erweiterte Logik-Familien: LVPECL, CML, VML und LVDS

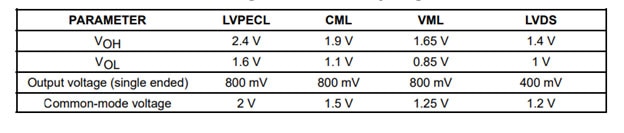

In Highspeed-Kommunikationssystemen werden Logikfamilien wie LVPECL (Low Voltage Positive Emitter Coupled Logic), CML (Current Mode Logic) und VML (Voltage Mode Logic) verwendet (Tabelle 1). Diese bieten schnellere Übergänge und eine bessere Störfestigkeit, erfordern aber ein sorgfältiges Design:

- LVPECL: Betrieb bei 3 V, mit Differenzsignalen und Highspeed-Performance

- CML: Verwendung von Konstantstromquellen für schnelles Schalten und geringen Jitter

- VML: Weniger gebräuchlich, bietet aber eine Signalisierung im Spannungsmodus mit lastunabhängigem Hub

- LVDS: Weit verbreitet für Differenzsignalübertragung mit moderater Geschwindigkeit und geringem Stromverbrauch

Tabelle 1: Spannungsparameter nach Logikpegel LVPECL, CML, VML und LVDS. (Quelle: Texas Instruments)

Tabelle 1: Spannungsparameter nach Logikpegel LVPECL, CML, VML und LVDS. (Quelle: Texas Instruments)

Bewährte Vorgehensweisen für I/O-Schnittstellen

- Prüfen Sie immer die Datenblätter auf VIH-, VIL-, VOH- und VOL-Werte.

- Verwenden Sie Pegelwandler, wenn Sie verschiedene Spannungsbereiche miteinander verbinden.

- Testen Sie frühzeitig und häufig mit Oszilloskopen und Logikanalysatoren.

Bei der I/O-Schnittstelle geht es nicht nur um das Verbinden von Pins, sondern auch darum, dass jedes Signal genau so verstanden wird, wie es gemeint ist. Da eingebettete Systeme immer komplexer werden und über mehrere Spannungsdomänen und Logikfamilien hinweg arbeiten, wird die Beherrschung der I/O-Kompatibilität immer wichtiger.

Durch das Verständnis von Spannungsstandards, die Vorwegnahme von Diskrepanzen und die Anwendung von bewährten Methoden können wir robuste, zuverlässige Systeme entwickeln, die klar und ohne Übersetzungsfehler kommunizieren. Wenn es jedoch erforderlich ist, ICs mit unterschiedlichen I/O-Standards zu verbinden, besteht eine Möglichkeit zur Abschwächung von Fehlanpassungen in der Verwendung von Pegelwandlern.

Pegelwandler

Ein Pegelwandler (LS) (auch als Spannungsübersetzer bekannt) ist eine Schaltung, die in eingebetteten Systemen verwendet wird, um eine sichere Schnittstelle zwischen Komponenten mit unterschiedlichen Spannungspegeln zu schaffen. Angenommen, ein mit 3,3 V betriebener Mikrocontroller muss mit einem Sensor kommunizieren, der mit einer 1,8V-Logik arbeitet. Der Pegelwandler sorgt dafür, dass die Signale korrekt zwischen den beiden übertragen werden, ohne dass die Gefahr einer Beschädigung oder eines logischen Fehlers besteht. Je nach verwendetem Protokoll können Pegelwandler als unidirektional oder bidirektional kategorisiert werden. Pegelwandler werden in der Regel mit MOSFETs, Puffer-ICs oder speziellen Übersetzerchips realisiert. Sie spielen eine wesentliche Rolle bei der Aufrechterhaltung der Signalintegrität und beim Schutz von Komponenten in Mischspannungsumgebungen.

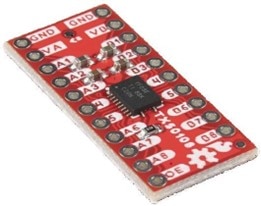

Abbildung 4: Achtkanaliges Pegelwandler-Modul. (Quelle: SparkFun)

Abbildung 4: Achtkanaliges Pegelwandler-Modul. (Quelle: SparkFun)

Zusätzliche Ressourcen

Have questions or comments? Continue the conversation on TechForum, Digi-Key's online community and technical resource.

Visit TechForum