Erweitern des Speichers winziger IoT- und Wearable-Designs mit HyperBus zur Platz- und Kostenersparnis

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2018-08-01

Da IoT-Knoten und Wearable-Geräte immer kleiner werden, müssen Entwickler den On-Board-Speicher ihrer Mikrocontroller optimal nutzen, um den benötigten Kartenplatz, den Stromverbrauch und die Kosten zu minimieren. Dennoch kann eine Speichererweiterung nicht immer vermieden werden. Statt standardmäßig die Busstruktur eines 32-Bit-Controllers zu verwenden, sollten Entwickler die Verwendung von HyperBus in Erwägung ziehen, einer 8-Bit-DDR-Highspeed-Schnittstelle mit 333 Mbit/s sowohl für Adress- als auch für Dateninformationen.

So sehr Entwickler auch versuchen, Speichererweiterungen zu vermeiden, sind sie aufgrund von während der Entwicklung gestiegenen Speicheranforderungen häufig nötig. Oder die Entwickler möchten das Design schlicht und ergreifend zukunftssicher machen, indem sie den künftigen Erweiterungsbedarf antizipieren.

Mit HyperBus können Mikrocontroller im Vergleich zum 16-Bit-Daten- und 16-Bit-Adressbus sowie den zugehörigen Steuerungs-Pins einer typischen 32-Bit-Schnittstelle an demselben Bus externen Flash-Speicher und RAM unterstützen. Möglich ist dies mit jedem Speichergerät mit HyperBus-Schnittstelle, einer effektiven, benutzerfreundlichen Schnittstelle für Speichererweiterungen mit geringer Pin-Anzahl in Anwendungen mit begrenzten Platzverhältnissen.

Obwohl der Busbetrieb für Firmware transparent ist, sollten sich Entwickler, die noch keinerlei Erfahrung mit HyperBus haben, zuerst mit dem Betrieb der Highspeed-Bussignale vertraut machen, um ein robustes Design gewährleisten zu können. In diesem Artikel wird zuerst der Betrieb von HyperBus beschrieben. Anschließend werden Mikrocontroller mit dieser Schnittstelle vorgestellt und es wird gezeigt, wie Benutzer sie effizient einsetzen und ihre Designs testen können.

So funktioniert HyperBus

Wie bereits erwähnt kommt bei HyperBus sowohl für die Übertragung von Adress- als auch von Dateninformationen eine 8-Bit-DDR-Highspeed-Schnittstelle zum Einsatz. Des Weiteren werden ein differenzieller Takteingang, ein Latch-Signal für Lese- und Schreibvorgänge sowie eine Chipwahl für jedes einzelne Speichergerät verwendet. HyperBus unterstützt externen Flash-Speicher und RAM am selben Bus und kann mit jedem Mikrocontroller mit HyperBus-kompatibler Peripherieschnittstelle verwendet werden.

HyperBus ist als eine Master/Slave-Schnittstelle konzipiert, bei der ein Master (Host) mit einem oder mehreren Slave-Speichergeräten am Bus verbunden ist. HyperBus-Flash-Speichergeräte werden als HyperFlash™ bezeichnet und HyperBus-DRAM-Speichergeräte als HyperRAM™.

Der Bus nutzt einen differenziellen Takteingang mit den Signalen CK und CK#. Da es sich bei HyperBus um eine DDR-Schnittstelle handelt, werden Daten sowohl an steigenden als auch an fallenden Taktflanken übertragen. Der Takt wird nur vom Master vorgegeben und seine Frequenz darf die Nenntaktfrequenz des langsamsten HyperBus-Speichers am Bus nicht überschreiten.

Der bidirektionale 8-Bit-Bus trägt die Bezeichnung DQ[0-7] und überträgt Adress-, Daten- und Befehlsinformationen zwischen den Master- und Slave-Geräten. Ein bidirektionales Strobe-Signal zum Lesen und Schreiben von Daten (RWDS) wird zur Speicherung von Daten verwendet. Das RWDS-Signal wird von jedem Gerät geregelt, das Daten liest. Wenn also der Mikrocontroller-Host Daten in das HyperRAM schreibt, regelt das HyperRAM das RWDS-Signal. Die an DQ[0-7] gelesenen Daten werden an beiden Taktflanken ausgerichtet.

Jedes Slave-Gerät wird über Chipauswahl-Signale (Aktiv-Low) ausgewählt, die mit CS0#, CS1#, CS2# usw. bezeichnet sind. Es kann immer nur eine Chipauswahl aktiv sein. Alle Bustransaktionen werden initiiert, wenn das jeweilige Chipauswahlsignal von „High-Pegel“ zu „Low-Pegel“ wechselt. Alle Bustransaktionen werden beendet, wenn das jeweilige Chipauswahlsignal von „Low-Pegel“ zu „High-Pegel“ wechselt. Die Entwickler müssen dafür sorgen, dass zu jedem Zeitpunkt ein Chipauswahlsignal aktiv ist. Tun sie dies nicht, kann es passieren, dass mehrere HyperBus-Slave-Geräte gleichzeitig das RWDS-Signal treiben, was zu einer Korruption der Daten führen kann.

Der Master treibt ein Reset-Signal (Aktiv-Low) mit der Bezeichnung RESET# zum Zurücksetzen der Hardware. Wird es auf „Low“ gezogen, setzt das Signal den Status aller externen HyperBus-Speichergeräte zurück, die mit dem Signal verbunden sind. Dabei werden auch die internen Konfigurationsregister des Speichergeräts zurückgesetzt. Der Status des internen Speichers der HyperBus-Speichergeräte ist jedoch nicht betroffen. Bei den meisten HyperBus-Master-Mikrocontrollerschnittstellen ist RESET# nicht Bestandteil des HyperBus-Peripheriegeräts, sondern stattdessen ein allgemeiner I/O-Pin. HyperBus-Slave-Geräte verfügen über einen geringen Pullup am RESET#-Pin. Wenn er also unbelegt bleibt, wird er auf „High“ gezogen.

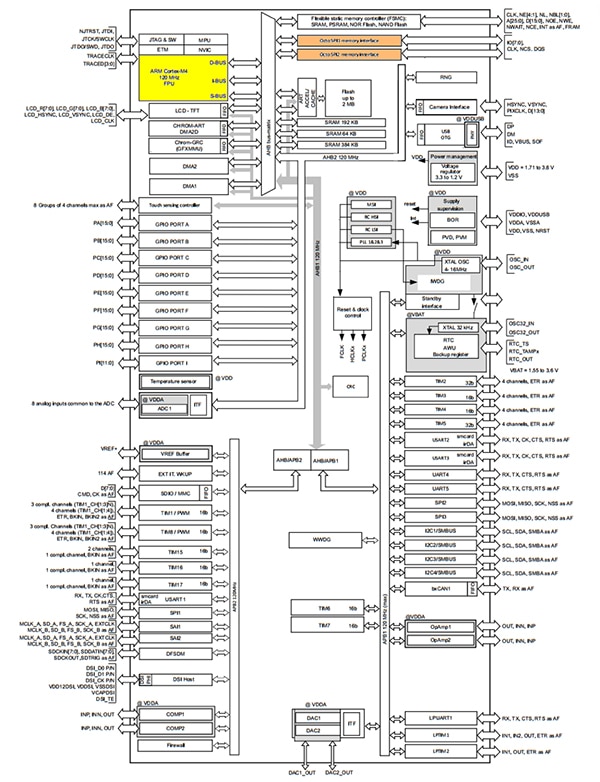

Jedes HyperBus-kompatible Peripheriegerät an einem Mikrocontroller muss der HyperBus-Spezifikation entsprechen. Ein gutes Beispiel für einen HyperBus-kompatiblen Mikrocontroller ist der STM32L4R9 Arm® Cortex®-M4F von STMicroelectronics (Abbildung 1). Der STM32L4R9 verfügt über 2 MB internen Flash-Speicher und 640 KB SRAM. Er bietet eine Vielzahl von Peripheriegeräten, einschließlich zwei OctoSPI-Schnittstellen, die als HyperBus-Schnittstellen konfigurierbar sind.

Der Mikrocontroller STMicroelectronics STM32F4L9 basiert auf einem Arm®-Cortex®-M4-Kern mit FPU und verfügt über zwei HyperBus-kompatible Schnittstellen (orange markiert). (Bildquelle: STMicroelectronics)

Der STM32L4R9 greift auf die externen Speicheradressen von HyperBus als Speicher zu, der auf den Adressraum des AHB-Busses des Mikrocontrollers abgebildet ist. Lese- und Schreibzugriffe auf den externen Speicher werden vom Kern also auf dieselbe Weise wie bei internem Speicher durchgeführt. Sobald die externen Speichergeräte konfiguriert sind, ist der Betrieb von HyperBus für den Kern transparent.

Bei HyperBus-Speichern handelt es sich um Speicher mit 16-Bit-Datenbreite. Jeder Zugriff vom STM32L4R9 muss daher innerhalb dieser 16-Bit-Speichergrenzen erfolgen. Datenzugriffe vom STM32L4R9-Master können als 16-Bit- oder 32-Bit-Zugriff erfolgen und müssen daher ebenfalls an den Grenzen ausgerichtet sein.

Eine typische Lese- oder Schreibtransaktion an HyperBus umfasst eine Sequenz von 16-Bit-Datenübertragungen innerhalb einer Taktperiode über zwei entsprechende 8-Bit-Datenübertragungen innerhalb einer halben Taktperiode, eine davon an jeder Taktflanke oder differenziellen Taktkreuzung. Lese- und Schreibtransaktionen übertragen immer vollständige 16-Bit-Datenwörter. Datenwörter von Lesetransaktionen enthalten immer zwei gültige Byte. Bei Datenwörtern von Schreibtransaktionen kann es sein, dass ein oder beide Byte maskiert sind, um zu verhindern, dass innerhalb eines Schreib-Burst einzelne Byte geschrieben werden. Byte-Übertragungen werden vom HyperBus-Protokoll nicht unterstützt. Gleiches gilt für Vorgänge wie Bit-Banding.

Jeder HyperBus-kompatible Port des STM32L4R9 verfügt über einen 256 MB großen, speicherabgebildeten Adressraum, der folgendermaßen abgebildet wird:

HyperBus1 (OctoSPI1) 0x90000000 bis 0x9FFFFFFF

HyperBus2 (OctoSPI2) 0x70000000 bis 0x7FFFFFFF

Die interne Adresse des HyperFlash- oder HyperRAM-Speichergeräts, auf das zugegriffen wird, wird von der Basisspeicheradresse des obigen Speicherorts abgeleitet. Wenn der STM32F4L9 beispielsweise einen Lesevorgang für den Speicherort 0x90000047 durchführt, liest er den im Speichergerät, auf das an HyperBus1 zugegriffen wird, am Speicherort 0x0047 gespeicherten Wert zurück.

Cypress Semiconductor hat sowohl die HyperBus-Spezifikation als auch eine Produktlinie mit HyperBus-Speichern entwickelt. Der HyperFlash-Speicher S26KS512SDPBHI020 (64 MB x 8) von Cypress kann problemlos mit einem der OctoSPI-Ports verbunden werden. Er unterstützt Wrap-Burst-Zugriffe mit bis zu 32 16-Bit-Wörtern. Mit einer maximalen Taktrate von 166,6 MHz unterstützt der S26KS512 HyperFlash die komplette anhaltende Leserate von 333 MB/s. Bei der maximalen Taktrate des OctoSPI-Ports von 60 MHz kann der STM32L4R9 jeden externen HyperBus-Speicher mit 120 MB/s (Maximalwert) lesen.

Der STM32L4R9 kann Code direkt aus diesem Flash-Speicher heraus ausführen, falls über den Cortex-M4-Systembus auf den HyperFlash zugegriffen wird. Bei Verwendung als Code-Speicher unterstützt der OctoSPI-Port eXecute In Place (XIP) mit einem integrierten Prefetch-Puffer, der die nächste Speicheradresse aus dem externen Speicher lädt.

Der HyperRAM-Speicher S27KS0641DPBHI020 (8 MB x 8) von Cypress Semiconductor ist ein Self-Refresh-DRAM, mit dem der Datenspeicher des STM32L4R9 erweitert werden kann. Er unterstützt Wrap-Burst-Zugriffe mit bis zu 64 16-Bit-Wörtern. Der S27KS0641 HyperRAM unterstützt außerdem anhaltende Leseraten von bis zu 333 MB/s und kann vom STM32L4R9 mit maximal 120 MB/s gelesen werden.

Anschließen von HyperBus-Speichern

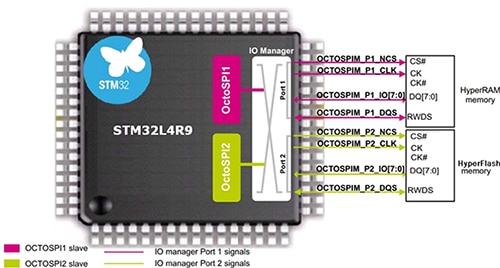

Der STM32L4R9 verfügt über zwei HyperBus-kompatible Ports. An jeden davon können jeweils separat externe HyperRAM- und HyperFlash-Speichergeräte angeschlossen werden (Abbildung 2). Das RESET#-Signal ist optional und in der Abbildung daher nicht enthalten. Sowohl mit dem HyperFlash als auch dem HyperRAM von Cypress kann der interne Speicher des STM32L4R9 problemlos und mit minimalen Auswirkungen auf Leiterplattengröße und Designkomplexität erweitert werden.

Abbildung 2: Der STM32L4R9 verfügt über zwei HyperBus-kompatible Ports. An jeden davon können jeweils separat externe HyperRAM- und HyperFlash-Speichergeräte angeschlossen werden. (Bildquelle: STMicroelectronics)

Die wichtigsten Signale für das Layout sind DQ[0-7] und RWDS. Für optimale Leistung sollte der Weg zwischen Mikrocontroller und Speicher für diese Signale auf der Leiterplatte so kurz wie möglich sein.

Die differenziellen Taktsignale CK und CK# sollten nebeneinander liegen mit konstantem Abstand zwischen ihnen für die Dauer des Signals. Sofern möglich, sollten Sie CK und CK# mit VSS abschirmen, um EMI zu minimieren. Zur Minimierung von Impedanz-Fehlanpassungen sollten alle Signale auf der obersten Schicht der Leiterplatte liegen mit einer festen VSS-Schicht darunter.

Entwickler, die noch nicht mit HyperBus gearbeitet haben, sollten Prüfpunkte für Messfühler einplanen. Für DQ[0-7] und RWDS sollten sich sowohl am Mikrocontroller STM32L4R9 als auch am Speichergerät Prüfpunkte befinden. Wenn der STM32L4R9 einen Schreibvorgang ausführt, sollten die Prüfpunkte betrachtet werden, die sich am nächsten am Speichergerät befinden. Wenn der STM32L4R9 einen Lesevorgang ausführt, sollten die Prüfpunkte betrachtet werden, die sich am nächsten am STM32L4R9 befinden. Positionieren Sie die Prüfpunkte für CK, CK# und CS näher am Speichergerät.

Aufgrund der hohen Taktfrequenzen im Zusammenhang mit der DDR-Schnittstelle muss die Spannungsversorgung des STM32L4R9 und der Speichergeräte so rauscharm wie möglich sein. Eine Versorgung mit starkem Rauschen beeinträchtigt den Signaltakt und kann Busübertragungsfehler verursachen. Es wird daher empfohlen, Entkopplungskondensatoren zu verwenden. HyperBus-Speichergeräte verfügen für die I/O-Pins über eine separate Stromversorgung und Masse und auf der oberen oder der unteren Schicht sollten Kondensatoren mit 1 Mikrofarad (µF) und 0,1 µF zur I/O-Versorgungsspannung VCCQ hinzugefügt werden.

Firmware-Zugriff auf HyperBus

HyperBus-Speichergeräte verfügen über On-Chip-Register, die zum Festlegen von Optionen und Takten für das Gerät verwendet werden. HyperBus bezeichnet diese Register als Konfigurationsregister (CR). Alle HyperRAM-Geräte verfügen über interne CRs, über die bestimmte Betriebsmerkmale eingestellt werden können. Für den HyperRAM S27KS0641 können mit der Firmware die Energiesparmodi, Wrap-Burst-Länge, Wrap-Burst-Typ, Timing-Parameter für das Lesen und Schreiben sowie die Ansteuerungsstärke am Ausgang des externen 8-Bit-Datenbusses konfiguriert werden.

HyperFlash verfügt zwar nicht über CRs, dafür aber über Statusregister. Der HyperFlash S26KS512 verfügt über drei Statusregister. Er unterstützt internen Fehlerkorrekturcode (Error Correction Code, ECC) zur Validierung von Schreibvorgängen und verfügt über ein ECC-Statusregister, um Schreibfehler anzuzeigen. Ein weiteres Register enthält die Adressen sämtlicher ECC-Fehler. Ein drittes Register zählt die ECC-Korrekturen und die nicht korrigierbaren Fehler. Alle diese Register sind schreibgeschützt.

HyperBus-Transaktionen unterstützen zwei Arten von Speicheroperationen. Bei der ersten handelt es sich um Lese- und Schreibvorgänge für externen Speicher. Bei der zweiten handelt es sich um Lese- und Schreibvorgänge für CRs oder das Lesen von Statusregistern.

Sobald der OctoSPI-Port des STM32L4L9 als HyperBus-Port konfiguriert ist, kann der Kern auf den Speicher wie auf jeden anderen speicherabgebildeten Speicherort auch zugreifen. Jeder Lese- oder Schreibvorgang im speicherabgebildeten HyperBus-Raum initiiert eine Transaktion zwischen dem Mikrocontroller und dem exernen Speicher. Jede HyperBus-Transaktion beginnt damit, dass der Mikrocontroller drei 16-Bit-Wörter mit Befehls-/Adressanweisungen an das externe Speichergerät sendet. Die Befehls-/Adresssequenz übermittelt dem externen Speichergerät, ob es sich um einen Lese- oder Schreibvorgang handelt, ob Speicherplatz oder Konfigurationsregister adressiert werden, ob es sich um eine Wrap- oder lineare Burst-Transaktion handelt und enthält Zeile und Spalte der Zieladresse. Obwohl all das für den Mikrocontroller über die Firmware transparent ist, spielt die Befehls-/Adresssequenz beim Debugging eine wichtige Rolle.

Erste Schritte mit HyperBus

Nachdem sich der Entwickler mit dem HyperBus-Protokoll vertraut gemacht hat, sollte er mit einer Evaluierungskarte einige experimentelle Programmierungen durchführen, insbesondere dann, wenn der Entwickler zuvor noch nie mit dieser Schnittstelle gearbeitet hat. Die Evaluierungskarte STM32L4R9I-EVAL von STMicroelectronics für den Mikrocontroller STM32L4R9 ist hierfür ein guter Ausgangspunkt (Abbildung 3). Das HyperRAM-Speichergerät ist rot eingekreist und die Prüfpunkte des Geräts befinden sich an der Steckleiste rechts.

Abbildung 3: Die STM32L4R9I-EVAL von STMicroelectronics wird zur Evaluierung des Mikrocontrollers STM32L4R9 verwendet. Das HyperRAM-Speichergerät ist rot eingekreist und die Prüfpunkte des Geräts befinden sich an der Steckleiste rechts. (Bildquelle: STMicroelectronics)

Die STM32L4R9I-EVAL hat einen großen Funktionsumfang und bietet unter anderem eine Kameraschnittstelle, zwei MEMS-Mikrofone, einen Joystick sowie ein TFT-LCD-Farbdisplay mit 4,3 Zoll und 480 x 272 Pixel. Die Evaluierungskarte unterstützt die OctoSPI-Schnittstelle und verfügt über das HyperRAM-Gerät IS66WVH8M8BLL mit 64 Mbit/s von ISSI, das auf die Leiterplatte gelötet ist.

Fazit

Das HyperBus-Protokoll ist eine geeignete, benutzerfreundliche Schnittstelle für Speichererweiterungen mit geringer Pin-Anzahl in Anwendungen mit begrenzten Platzverhältnissen. Obwohl der Busbetrieb für Firmware transparent ist, sollte sich ein Entwickler, der noch keinerlei Erfahrung mit HyperBus hat, zuerst mit dem Betrieb der Highspeed-Bussignale vertraut machen, um ein robustes Design gewährleisten zu können.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.