Aktivieren der NVMe-SSD-Schnittstelle auf einem Xilinx ZCU102-Evaluierungskit

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2020-05-12

Übersicht

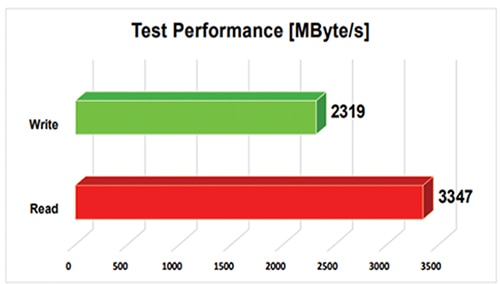

Die Zynq® UltraScale+™ MPSoC-Familie, basierend auf der Xilinx® UltraScale™ MPSoC-Architektur, integriert ein funktionsreiches 64-Bit Quad-Core oder Dual-Core ARM-basiertes Verarbeitungssystem (PS) und die Xilinx Programmable Logic (PL) UltraScale-Architektur in einem einzigen Baustein. Ebenfalls enthalten sind On-Chip-Speicher, externe Speicherschnittstellen mit mehreren Anschlüssen und eine Vielzahl von Schnittstellen für Peripheriegeräte, insbesondere ein GTH-Transceiver mit 16,3 Gbit/s, der eine PCI Express® Gen3-Speicherschnittstelle wie ein NVMe-SSD-Laufwerk unterstützen kann. Dieser Artikel demonstriert die Lösung der NVMe SSD (solid state drive) Schnittstellenimplementierung auf Xilinx's ZCU102 Evaluation Kit unter Verwendung des Design Gateway's NVMeG3-IP Core, der in der Lage ist, eine unglaublich schnelle Leistung zu erzielen: 2.319 MB/s Schreib- und 3.347 MB/s Lesegeschwindigkeit.

Einführung in das Zynq® UltraScale+ MPSoC ZCU102 Evaluierungskit

Der ZCU102 ist ein universell einsetzbares Evaluierungsboard für Rapid-Prototyping basierend auf dem XCZU9EG-2FFVB1156E MPSoC-Bauteil. Auf der Baugruppe befinden sich ein Hochgeschwindigkeits-DDR4-SODIMM und Bausteinspeicherschnittstellen, FMC-Erweiterungsports, serielle Multi-Gigabit-pro-Sekunde-Transceiver, eine Vielzahl von Peripherieschnittstellen und FPGA-Logik für anwenderspezifische Designs, die alle eine flexible Prototyping-Plattform bieten.

Abbildung 1: ZCU102-Evaluierungskit. (Bildquelle: Xilinx Inc.)

Abbildung 1: ZCU102-Evaluierungskit. (Bildquelle: Xilinx Inc.)

Der ZCU102 bietet programmierbare Logikfunktionen für die Erstellung hochmoderner Anwendungen wie 5G Wireless, fortschrittliche Fahrerassistenzsysteme der nächsten Generation (ADAS) und industrielle Lösungen für das Internet der Dinge (IIoT).

Wie auch immer, für die Anwendung, die eine externe Datenspeicherung mit hoher Leistung und hoher Zuverlässigkeit erfordert, wie NVMe SSD-Laufwerke, wird die richtige Lösung benötigt, die die Vorteile der GTH Transceiver for PCI Express® Gen3 Compliance-Schnittstelle nutzt.

Einführung in die NVMe SSD-Speicherung

NVM Express (NVMe) definiert die Schnittstelle, auf die der Host-Controller per PCI Express als SSD zugreifen kann. NVM Express optimiert die Ausgabe des Befehls und den Abschluss des Prozesses durch die Verwendung von nur zwei Registern (Befehlsausgabe und Befehlsabschluss). Ansonsten unterstützt NVMe den Parallelbetrieb durch die Unterstützung von bis zu 64K-Befehlen innerhalb einer einzigen Warteschlange. 64K-Befehlseingaben verbessern die Übertragungsleistung sowohl bei sequentiellem als auch bei wahlfreiem Zugriff.

NVMe-Laufwerke haben den Weg für Datenspeicherung und Berechnungen mit sehr hohen Geschwindigkeiten geebnet. Durch den Einsatz der PCIe Express® Gen3-Technologie können moderne NVMe SSD-Laufwerke Geschwindigkeiten von bis zu 40 Gbit/s Spitzenleistung erreichen.

Ein Beispiel für ein NVMe-Speichergerät wird hier gezeigt.

Implementierung eines NVMe-Host-Controllers auf dem ZCU102

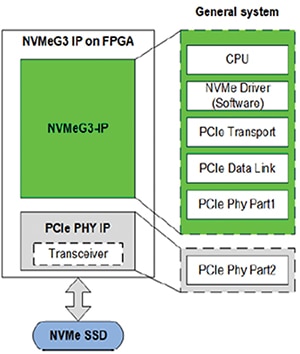

Abbildung 2: NVMe Implementierung. (Bildquelle: Design Gateway)

Abbildung 2: NVMe Implementierung. (Bildquelle: Design Gateway)

Konventionell wird der NVMe-Host unter Verwendung eines Host-Prozessors, der mit einem PCIe-Controller arbeitet, für die Übertragung von Daten zum und vom NVMe-SSD implementiert. Das NVMe-Protokoll ist für die Gerätetreiber-Kommunikation mit der PCIe-Controller-Hardware-CPU-Peripherie implementiert, die über einen sehr schnellen Bus verbunden ist. Externer DDR-Speicher ist für die Datenpufferung und die Befehlswarteschlange zur Übertragung der Daten zwischen dem PCIe-Controller und dem SSD erforderlich.

Da ein integrierter PCIe-Gen3-Block auf einem XCZU9EG-2FFVB1156E-FPGA-Baustein auf dem ZCU102 nicht verfügbar ist, ist ein konventioneller Implementierungsansatz nicht möglich.

Design Gateway schlägt eine Lösung vor, bei der der NVMeG3-IP Core, wie in Abbildung 2 dargestellt, verwendet wird, um eine NVMe SSD-Schnittstelle für ein Zynq® UltraScale+™ MPSoC-Gerät zu aktivieren, für das kein integrierter PCIe-Block verfügbar ist. Die NVMe-Schnittstelle für den ZCU102 ermöglicht den Aufbau eines Mehrkanal-RAID-Systems mit sehr hoher Leistung und geringstmöglichem FPGA-Ressourcenverbrauch. Die NVMeG3-IP-Kernlizenz enthält das Beispiel-Referenzdesign, das Designern hilft, Entwicklungszeit und -kosten zu reduzieren.

Überblick über NVMeG3-IP von Design Gateway

NVMe IP Core mit PCIe Gen3 Soft IP (NVMeG3-IP) ist ideal für den Zugriff auf eine NVMe SSD ohne integrierten PCIe-Block, CPU und externen Speicher. NVMeG3-IP umfasst PCIe Gen3 Soft IP und 256 Kbyte Speicher. Diese Lösung wird für die Anwendung empfohlen, die NVMe SSD-Speicher mit Ultra-Hochgeschwindigkeitsleistung erfordert, indem ein kostengünstiger FPGA verwendet wird, der keinen integrierten PCIe-Block enthält.

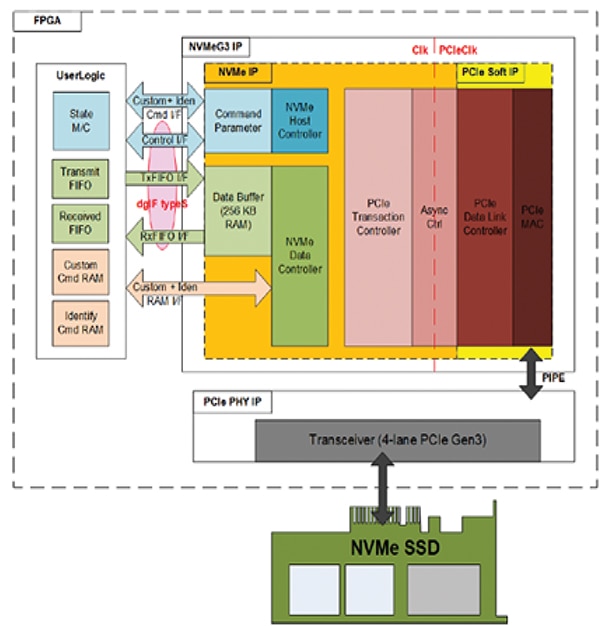

Abbildung 3: NVMeG3-IP-Blockdiagramm. (Bildquelle: Design Gateway)

Abbildung 3: NVMeG3-IP-Blockdiagramm. (Bildquelle: Design Gateway)

Eigenschaften von NVMeG3-IP

NVMeG3-IP verfügt über viele Funktionen, von denen einige im Folgenden hervorgehoben werden:

- Implementierung der Anwendungsschicht, der Transaktionsschicht, der Datenverbindungsschicht und einiger Teile der physischen Schicht, um ohne CPU-Nutzung auf das NVMe SSD zuzugreifen.

- Betrieb mit Xilinx PCIe PHY IP konfiguriert als 4-Lane PCIe Gen3 (128-Bit-Bus-Schnittstelle)

- Einschließlich 256 Kbyte RAM-Datenpuffer

- Einfache Benutzeroberfläche über dgIF typeS

- Unterstützt sechs Befehle, d.h. Identify, Shutdown, Write, Read, SMART und Flush (Unterstützung zusätzlicher Befehle als Option)

- Unterstütztes NVMe-Gerät:

- Code der Basisklasse:01h (Massenspeicher), Code der Unterklasse:08h (nichtflüchtig), Programmierschnittstelle:02h (NVMHCI)

- MPSMIN (Mindestspeicherseitengröße): 0 (4Kbyte)

- MDTS (Maximale Datentransfergröße): Mindestens 5 (128 Kbyte) oder 0 (keine Beschränkung)

- LBA-Einheit: 512 Byte oder 4096 Byte

- Die Benutzer-Taktfrequenz muss größer oder gleich dem PCIe-Takt sein (250MHz für Gen3)

- Verfügbares Referenzdesign:

- ZCU102 mit AB17-M2FMC-Adapterkarte

- KCU105 mit Adapterplatine AB18-PCIeX16/AB16-PCIeXOVR

- VCU118 mit Adapterplatine AB18-PCIeX16

Design Gateway hat den NVMeG3-IP entwickelt, der als NVMe-Host-Controller für den Zugriff auf eine NVMe-SSD ausgeführt wird. Die Benutzeroberfläche und die Standardfunktionen sind auf eine einfache Bedienung ausgelegt, ohne dass Kenntnisse des NVMe-Protokolls erforderlich sind. Das zusätzliche Merkmal von NVMeG3-IP ist die eingebaute PCIe-Soft-IP, die die Datenverbindungsschicht und einige Teile der physikalischen Schicht des PCIe-Protokolls durch reine Logik implementiert. So kann NVMeG3-IP in einem FPGA, der keinen integrierten PCIe-Block hat, unter Verwendung der eingebauten PCIe-Soft-IP und des Xilinx PCIe PHY IP-Kerns betrieben werden. Xilinx PCIe PHY IP ist ein frei verfügbarer IP-Kern, der einen Transceiver und einen logischen Equalizer enthält.

NVMeG3-IP unterstützt sechs NVMe-Befehle, d.h. Identifizieren, Herunterfahren, Schreiben, Lesen, SMART und Spülen. 256 Kbyte BlockRAM sind in den NVMeG3-IP integriert und dienen als Datenpuffer. Das System benötigt keine CPU und keinen externen Speicher. Weitere Einzelheiten zum NVMeG3-IP sind in seinem Datenblatt beschrieben, das von unserer Website heruntergeladen werden kann.

Die Verwendung von FPGA-Ressourcen auf dem FPGA-Baustein XCZU9EG-2FFVB1156E ist in Tabelle 1 unten dargestellt.

|

Tabelle 1: Beispiel-Implementierungsstatistik für Ultrascale/Ultrascale+-Gerät

Implementierung und Leistungsergebnis auf ZCU102

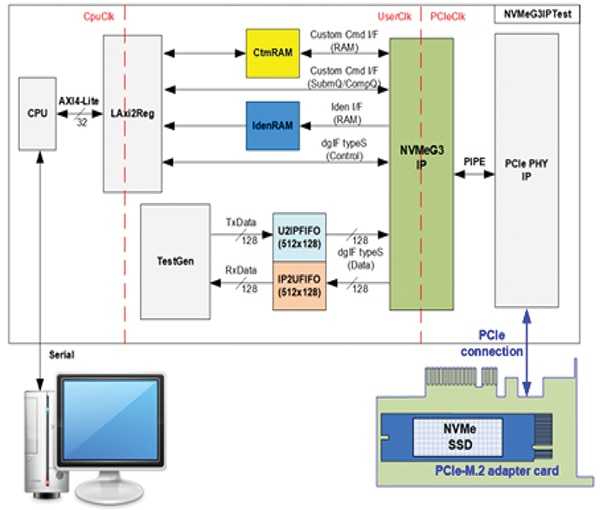

Abbildung 4 zeigt die Übersicht des Referenzdesigns auf der Grundlage des ZCU102 zur Demonstration des NVMeG3-IP-Betriebs. Das Modul NVMeG3IPTest im Demosystem umfasst folgende Module: TestGen, LAxi2Reg, CtmRAM, IdenRAM und FIFO.

Weitere Einzelheiten zum NVMeG3-IP-Referenzdesign finden Sie im NVMeG3-IP-Referenzdesign-Dokument auf der Website von Design Gateway.

Abbildung 4: NVMeG3-IP Referenzdesign Übersicht. (Bildquelle: Design Gateway)

Abbildung 4: NVMeG3-IP Referenzdesign Übersicht. (Bildquelle: Design Gateway)

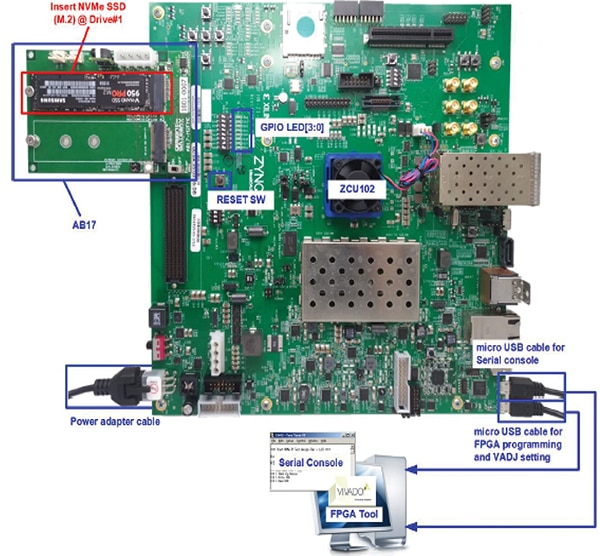

Das Demosystem ist für das Schreiben/Verifizieren von Daten mit der NVMe-SSD auf dem ZCU102 ausgelegt. Der Benutzer steuert den Testvorgang über eine serielle Konsole. Für die Schnittstelle des NVMe-SSD mit dem ZCU102 ist eine AB17-M2FMC-Adapterkarte erforderlich, wie in Abbildung 5 dargestellt.

Abbildung 5: NVMeG3-IP-Demoumgebung auf ZCU102 eingerichtet. (Bildquelle: Design Gateway)

Abbildung 5: NVMeG3-IP-Demoumgebung auf ZCU102 eingerichtet. (Bildquelle: Design Gateway)

Das Beispiel-Testergebnis beim Ausführen des Demosystems auf dem ZCU102 unter Verwendung des 512 GB Samsung 970 Pro ist in Abbildung 6 dargestellt.

Abbildung 6: NVMe SSD-Lese-/Schreibleistung auf ZCU102 unter Verwendung von Samsung 970 PRO S. (Bildquelle: Design Gateway)

Abbildung 6: NVMe SSD-Lese-/Schreibleistung auf ZCU102 unter Verwendung von Samsung 970 PRO S. (Bildquelle: Design Gateway)

Fazit

NVMeG3-IP Core bietet eine Lösung zur Aktivierung der NVMe SSD-Schnittstelle auf dem ZCU102-Evaluierungskit und auch die Lösung für die Zynq® UltraScale+™ MPSoC-Gerätefamilie von Xilinx®, wo ein integrierter PCIe-Block nicht verfügbar ist. NVMeG3-IP wurde mit dem Ziel entwickelt, die höchstmögliche Leistung bei geringstmöglichem FPGA-Ressourcenverbrauch für den NVMe SSD-Zugriff zu erreichen, ohne dass eine CPU erforderlich ist. Er eignet sich sehr gut für hochleistungsfähige NVMe-Speicher ohne CPU-Einsatz und ist in der Lage, mehrere NVMe-SSD-Schnittstellen zu implementieren, indem GTH-Transceiver ohne Einschränkungen durch die Anzahl der verfügbaren integrierten PCIe-Blöcke auf dem FPGA-Baustein verwendet werden.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.