Warum der Inter-Integrated Circuit (I2C)-Bus den Anschluss von ICs so einfach macht - und wie man ihn verwendet

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2020-04-07

Die Kommunikation und Steuerung zwischen integrierten Schaltungen mit Hilfe eines parallelen Busses auf einer Leiterplatte (pc board) ist nicht praktikabel. Selbst ein 8-Bit-Prozessor würde 16 Leitungen allein für Daten und noch viel mehr für einen Adressbus benötigen. Noch problematischer ist es, wenn sich mehrere ICs an einem gemeinsamen Kommunikationsbus befinden müssen. Es gibt nicht genug Platz für all diese Leiterplatten-Trace-Läufe. Die Lösung ist die Verbindung von ICs über einen seriellen Kommunikationsbus wie den Inter-Integrated Circuit (I2C) Bus, einen seriellen Zweidraht-Bus, der dieses Problem löst.

Dieser Artikel beschreibt die Ursprünge des I2C-Busses und wie er funktioniert, um eine effiziente serielle Verbindung zwischen den ICs herzustellen. Anschließend wird erörtert, wie der I2C-Bus physikalisch implementiert ist, die Protokollstruktur und allgemeine Anwendungen dieses allgegenwärtigen Kommunikationsbusses. Beispiel I2C Schnittstellen und Lösungen von Microchip Technology werden zu Demonstrationszwecken verwendet. Der Artikel behandelt auch I2C Ähnlichkeiten und Unterschiede mit dem System Management Bus (SMBus).

Was ist der I2C-Bus?

Der I2C-Bus wurde Anfang der 1980er Jahre von Phillips Semiconductors, jetzt NXP Semiconductors, als einfacher bidirektionaler Zweidraht-Bus für effiziente Kommunikation und Steuerung von integrierten Schaltungen auf einer gemeinsamen Leiterplatte entwickelt. Die erste Spezifikation wurde 1992 fertiggestellt, und der Bus hat sich seitdem zu einem De-facto-Standard entwickelt, der in Komponenten von über 50 IC-Herstellern angeboten wird. Dieser umfangreiche Einsatz ermöglicht einen Systemansatz für das Design, bei dem ICs ohne weiteres in die I2C-Busstruktur aufgenommen werden können, ohne dass ein kundenspezifisches Design erforderlich ist. Mehrere andere spezialisierte Busse wie der SMBus und der Power Management Bus (PMBus) sowie mehrere andere teilen sich die Grundarchitektur.

Der I2C-Bus kann mehrere ICs und Sensoren miteinander verbinden, da es sich um einen adressierbaren Bus handelt; ein Sieben- oder Zehn-Bit-Adressfeld ermöglicht das Senden von Nachrichten an ein ausgewähltes Gerät durch das Master-Gerät. Die ursprüngliche I2C hatte eine maximale Taktrate von 100 Kilohertz (kHz), aber im Laufe der Jahre wurde diese Grenze durch höhere Geschwindigkeitsbetriebsarten auf 3,4 Megahertz (MHz) verschoben.

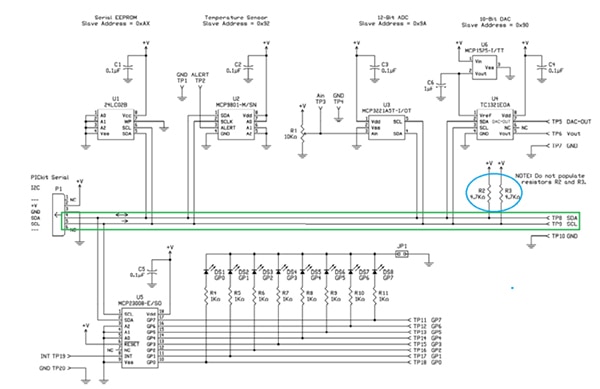

Der I2C-Bus verwendet zwei Drähte, die als serielle Datenleitung (SDA) und serielle Taktleitung (SCL) bezeichnet werden. SDA und SCL sind bidirektionale Open-Drain/Kollektor-Leitungen und werden über eine Stromquelle oder einen Pullup-Widerstand mit dem positiven Energiebus verbunden. Es können mehrere Geräte an den Bus angeschlossen werden, wobei die maximale Anzahl durch die Buskapazität begrenzt ist. Ein Master-Gerät steuert den Bus, und jedes Gerät auf dem Bus hat eine eindeutige Adresse. Das Master-Gerät kann sowohl Daten über den Bus senden als auch empfangen (Abbildung 1). I2C unterstützt Multi-Master-Betrieb mit Kollisionserkennung und Arbitrierung, um zu verhindern, dass zwei oder mehr Master-Geräte gleichzeitig Datenübertragungen initiieren. Dieser Artikel wird sich jedoch auf einzelne Master-Konfigurationen konzentrieren.

Abbildung 1: Schema einer Demonstrationsplatine von Microchip Technology, die den I2C-Bus implementiert und mit fünf verschiedenen Geräten verbindet. Das Master-Gerät ist über den Steckverbinder P1 von der Platine getrennt. Die SCL- und SDA-Linien sind grün umrandet, und die beiden Pullup-Widerstände sind blau eingekreist. (Bildquelle: Mikrochip-Technologie)

Abbildung 1: Schema einer Demonstrationsplatine von Microchip Technology, die den I2C-Bus implementiert und mit fünf verschiedenen Geräten verbindet. Das Master-Gerät ist über den Steckverbinder P1 von der Platine getrennt. Die SCL- und SDA-Linien sind grün umrandet, und die beiden Pullup-Widerstände sind blau eingekreist. (Bildquelle: Mikrochip-Technologie)

Abbildung 1 zeigt das Schema einer Mikrochip-Technologie PKSERIAL-I2C1 I2C Demonstrationsplatine. Diese Karte implementiert den I2C-Bus unter Verwendung von fünf verschiedenen Bausteinen, einschließlich eines EEPROMs, eines Temperatursensors, eines 12-Bit-Analog/Digital-Wandlers (ADC), eines 10-Bit-Digital/Analog-Wandlers (DAC) und eines 8-Bit-Seriell/Parallel-Wandlers. Das Master-Gerät befindet sich nicht auf der Platine und wird über den Steckverbinder P1 angeschlossen. Die SDA- und SCL-Busleitungen sind grün umrandet und die Pullup-Widerstände sind blau eingekreist.

Die SDA- und SCL-Pegel sind in der Regel ein fester Prozentsatz der positiven Versorgungsspannung, der üblicherweise als VDD bezeichnet wird. Die Referenzpegel sind auf 70% und 30% von VDD für die Logikpegel „1“ (HIGH-Pegel) bzw. Logik „0“ (LOW-Pegel) festgelegt.

Taktsignale treten in Bursts mit einem Takt für jedes übertragene Datenbit auf. Daten auf der SDA-Leitung müssen gültig sein, solange das Taktsignal einen HIGH-Pegel führt. Daten können nur geändert werden, solange das Taktsignal einen LOW-Pegel führt.

Aus der Sicht eines Designers werden neue Projekte vereinfacht, da die I2C-Schnittstellen in die ICs integriert sind und keine Notwendigkeit besteht, eine Schnittstelle zu entwerfen. Jedes Gerät wird einfach direkt an den Bus angeschlossen. ICs können dem Bus hinzugefügt oder entfernt werden, ohne die anderen Schaltungen zu beeinflussen (vorausgesetzt, die Anzahl der ICs insgesamt überschreitet nicht die Kapazitätsgrenze). Der einfache Zweidraht-Bus minimiert die Anzahl der Pins auf jedem IC und die Anzahl der Leiterbahnen auf der Platine.

Das I2C-Protokoll

Der Bus ist 8-Bit-orientiert und kommuniziert in Bytes. Wie bereits erwähnt, betrug die ursprüngliche maximale Taktrate 100 kHz im so genannten Standard-Modus. Der Bus unterstützt jetzt 400 Kilobit pro Sekunde (kbits/s) im Fast Mode, bis zu 1 Mega Bit pro Sekunde (Mbit/s) im Fast Mode Plus und bis zu 3,4 Mbits/s im High Speed Mode (Hs-Mode).

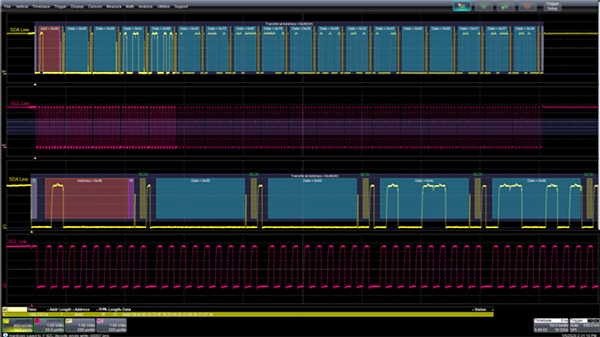

Das Protokoll I2C lässt sich am besten anhand einer typischen Übertragung auf dem Bus veranschaulichen (Abbildung 2). Die Quelle des Bildschirmbildes ist ein Teledyne LeCroy Oszilloskop mit seriellem Datentrigger mit niedriger Geschwindigkeit und Dekodieroption WS4KHD-EMB TD. Diese Oszilloskop-Option kann bis zu 19 serielle Datenschnittstellen mit niedriger Geschwindigkeit triggern und dekodieren, einschließlich I2C.

Abbildung 2: Ein typisches I2C Datenpaket, bestehend aus einem Startbit, einem Adressfeld, einem Bestätigungsbit, 17 Datenbytes mit jeweils einem eigenen ACK-Bit und schließlich einem Stoppbit. Jedes Feld ist durch ein farbcodiertes Overlay gekennzeichnet. Die obere (gelbe) Spur ist das gesamte SDA-Paket, darunter befindet sich die SCL-Uhr (rot). Die dritte und vierte Spur sind horizontal erweiterte Ansichten beider Signale. (Bildquelle: DigiKey)

Abbildung 2: Ein typisches I2C Datenpaket, bestehend aus einem Startbit, einem Adressfeld, einem Bestätigungsbit, 17 Datenbytes mit jeweils einem eigenen ACK-Bit und schließlich einem Stoppbit. Jedes Feld ist durch ein farbcodiertes Overlay gekennzeichnet. Die obere (gelbe) Spur ist das gesamte SDA-Paket, darunter befindet sich die SCL-Uhr (rot). Die dritte und vierte Spur sind horizontal erweiterte Ansichten beider Signale. (Bildquelle: DigiKey)

Das Oszilloskop kann bei bestimmten seriellen Ereignissen triggern, einschließlich Start, Stopp, fehlender Bestätigung (ACK), Adresse, Daten, Adresse plus Daten, Rahmenlänge und EEPROM-Datenübertragung. Die Protokollelemente des seriellen Datenstandards sind durch eine farbkodierte Überlagerung gekennzeichnet. Jedes Protokollfeld wird entweder binär, hex oder ASCII dekodiert, wobei der ausgewählte Code im Overlay angezeigt wird.

Das SDA-Signal erscheint als gelbe Kurve, während das SCL-Signal als rote Kurve angezeigt wird. Das graue Überlagerungsfeld zeigt die Start- und Stoppfunktionen an. Das ziegelrote Overlay markiert die Adressdaten, das blaue Feld die Paketdaten und die olivfarbenen Overlay-Boxen die ACK-Funktionen.

Der obere Trace zeigt das gesamte I2C SDA-Paket vom Start bis zum Stopp. Direkt darunter befindet sich das entsprechende SCL-Signal. Die dritte Abwärtsspur ist eine zeitgedehnte Zoomspur des SDA-Signals, und darunter befindet sich das synchrone SCL-Signal.

Sowohl die SDA- als auch die SCL-Leitung befinden sich zwischen den Übertragungen im High-Zustand, wenn der Bus frei ist. Das SCL-Signal besteht aus Bursts von neun Impulsen mit der Taktrate, einen für jedes übertragene Datenbit und einen zusätzlichen für das ACK-Bit.

Alle Bustransaktionen beginnen mit einem vom Master generierten Startbit, das in der gezoomten SDA-Spur als grau gefärbtes Überlagerungsfeld angezeigt wird. Der Start wird dadurch angezeigt, dass der Master die SDA-Leitung auf Low zieht, während sich die SCL-Leitung in einem High-Zustand befindet. Sobald der Master das Startbit ausgibt, gilt der Bus als belegt. Der Master kann mehrere Starts ausgeben, eine Situation, in der die nachfolgenden Starts oft als Neustarts bezeichnet werden.

Alle Datenübertragungen haben eine Länge von 8 Bit (ein Byte), jeweils gefolgt von einem ACK-Bit. Bits werden mit dem höchstwertigen Bit (MSB) zuerst übertragen. Jeder Byte-Transfer muss quittiert werden. Wenn das Slave-Gerät beschäftigt ist und keine Daten empfangen oder senden kann, kann es die SCL-Leitung nach unten ziehen. Dadurch wird das Master-Gerät in einen Wartezustand gezwungen, bis das Slave-Gerät die SCL-Leitung freigibt.

Das ACK-Bit wird gebildet, nachdem das sendende Gerät die SDA-Leitung vor dem neunten Bestätigungstakt freigibt. Wenn das empfangende Gerät das Datenbyte empfangen hat, zieht es die SDA-Leitung auf Low. In der Zoom-Ansicht des SDA in Abbildung 2 ist kurz vor dem neunten Taktimpuls eine schmale Spitze zu sehen, d.h. die SDA-Leitung wird freigegeben, um in den hohen Zustand zurückzukehren. Der Empfänger zieht die SDA-Linie nach unten und erzeugt so das ACK-Signal, das symbolisch durch die Überlagerung mit der Olivbox gekennzeichnet ist. Wenn der Empfänger die SDA-Leitung nicht vor dem neunten Takt herunterzieht, handelt es sich um eine "Not Acknowledge"-Antwort (NACK). Wenn ein NACK auftritt, kann der Master entweder ein Stoppsignal erzeugen und die Übertragung abbrechen oder einen erneuten Versuch starten.

Unmittelbar nach der Startbedingung wird eine Slave-Adresse ausgegeben. Dies wird durch einen ziegelroten Überlagerungskasten angezeigt. Es gibt zwei mögliche Adressformate; 7 Bit oder 10 Bit, wobei die 7-Bit-Adresse das gebräuchlichste ist. Die ersten 7 Bits nach dem Start stellen die Adressdaten dar. Das 8th Bit zeigt die Datenrichtung an - entweder Lesen oder Schreiben. Ein Schreibvorgang wird dadurch angezeigt, dass sich die SDA-Leitung in einem Low-Zustand befindet, während ein High-Zustand der SDA-Leitung zu diesem Zeitpunkt einen Lesevorgang anzeigt. Bei der 10-Bit-Adressierung werden die ersten beiden Bytes nach der Startbedingung verwendet. I2C reserviert mehrere Adressen für interne Funktionen. Die dekodierten Adressdaten erscheinen im Adress-Overly-Feld im Binär-, Hex- oder ASCII-Format.

Die blauen Überlagerungsfelder markieren die Datentransfers. Jede ist acht Bits lang und wird von einer ACK/NACK-Antwort gefolgt. Die Anzahl der Datenbytes in einem I2C-Paket ist unbegrenzt, aber Abbildung 2 enthält 17. Die dekodierten Daten erscheinen, wie die Adressdekodierung, im Datenüberlagerungsfeld. Dem Datenstrom folgt am Ende des Datentransfers ein vom Master generiertes Stoppbit, das durch ein graues Überlagerungsfeld in der oberen Datenspur angezeigt wird. Das Stoppbit ist ein LOW-zu-HIGH-Übergang auf der SDA-Leitung, während sich die SCL-Leitung im HIGH-Zustand befindet. Nach dem Haltesignal ist der Bus wieder frei.

Die Tabelle am unteren Rand der Anzeige fasst alle Informationen über das zugehörige Datenpaket zusammen, einschließlich der Zeit seit dem Trigger, der Adresslänge, der Adresse, der Lese- oder Schreiboperation, der Paketlänge und einer Zusammenfassung des Dateninhalts. Die Anzahl der Einträge in der Tabelle entspricht der Anzahl der vom Scope erfassten I2C-Pakete, die in diesem Fall nur eine einzige Zeile ist.

Wenn ein Protokollfehler auftritt, wird er durch ein leuchtend rotes Kästchen hinter den anderen Protokoll-Overlay-Boxen angezeigt.

I2C-Geräte

Einer der größten Vorteile des I2C-Busses ist die extrem große Anzahl von Geräten, die ihn in ihr Design integriert haben. Das Demoboard von Microchip Technologies bietet einige Beispiele für die Arten von ICs, die den I2C-Bus oder eines seiner Derivate wie den SMBus enthalten.

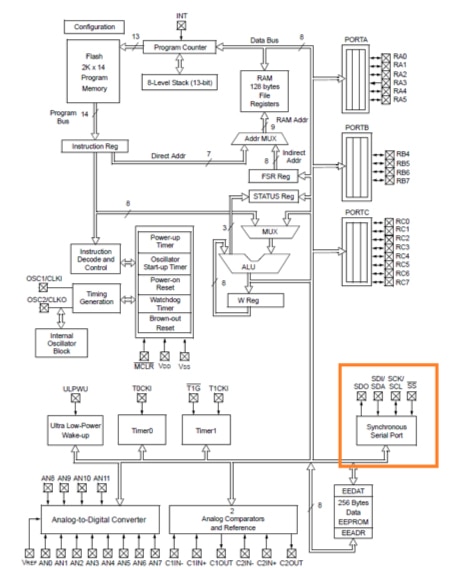

Der PIC16F677 von Microchip Technology ist ein 8-Bit-Mikrocontroller, der in vielen eingebetteten Designs Verwendung findet. Er implementiert eine synchrone serielle Schnittstelle, die so gesteuert werden kann, dass sie entweder mit der seriellen Peripherieschnittstelle (SPI) oder I2C zu anderen Controllern oder Peripheriegeräten kommuniziert (Abbildung 3).

Abbildung 3: Der Microchip Technology PIC16F677 ist ein 8-Bit-Mikrocontroller mit einer synchronen seriellen Schnittstelle (orange umrandet), die entweder als SPI- oder als I2C-Bus programmiert werden kann. (Bildquelle: Microchip Technology)

Abbildung 3: Der Microchip Technology PIC16F677 ist ein 8-Bit-Mikrocontroller mit einer synchronen seriellen Schnittstelle (orange umrandet), die entweder als SPI- oder als I2C-Bus programmiert werden kann. (Bildquelle: Microchip Technology)

Dieser Mikrocontroller unterstützt sowohl den Master- als auch den Slave-Modus von I2C mit 7- oder 10-Bit-Adressierung. Er verwendet den SCK/SCL-Pin für das I2C SCL-Taktsignal und den SDI/SDA-Pin für das Datensignal.

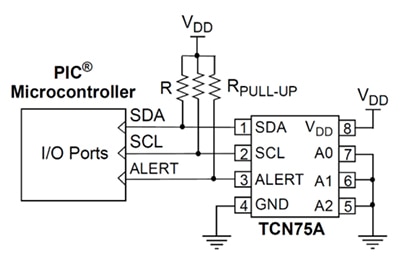

Diese beiden Pins sind mit den SCL- und SDA-Leitungen auf dem I2C-Bus verbunden, um die Kommunikation mit anderen Geräten zu ermöglichen. Ein üblicher Anschluss ist ein I2C-basierter Sensor wie z.B. der TCN75AVOA713 serielle Zweidraht-Temperatursensor von Microchip Technology (Abbildung 4).

Abbildung 4: Der Temperatursensor TCN75A von Microchip Technology ist direkt an den Mikrocontroller PIC16F677 angeschlossen, um Temperaturdaten zu übermitteln. (Bildquelle: Microchip Technology)

Abbildung 4: Der Temperatursensor TCN75A von Microchip Technology ist direkt an den Mikrocontroller PIC16F677 angeschlossen, um Temperaturdaten zu übermitteln. (Bildquelle: Microchip Technology)

Durch die Fähigkeit zur seriellen Kommunikation verfügt dieser Temperatursensor über eine erhöhte Funktionalität. Seine internen, vom Benutzer programmierbaren Register können zur Einstellung der Temperaturmessauflösung, des Stromspar-Abschaltmodus und sogar zur Einstellung des Alarmausgangs verwendet werden, um anzuzeigen, wenn der Temperaturbereich die voreingestellten Grenzen überschreitet.

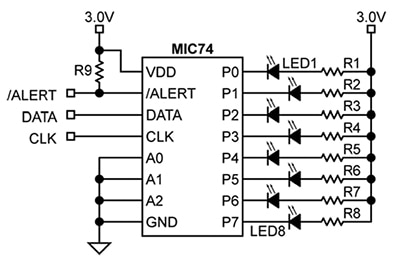

Es gibt auch eine Reihe von Geräten, die den seriellen Datenstrom I2C dekodieren und in parallele Daten aufbrechen. Betrachten Sie die Mikrochip-Technologie MIC74YQS-TR 2-Draht E/A-Expander und Lüftersteuerung (Abbildung 5).

Abbildung 5: Der E/A-Expander MIC74YQS-TR von Microchip Technology wandelt den seriellen Datenstrom in acht unabhängige parallele E/A-Leitungen um. (Bildquelle: Microchip Technology)

Abbildung 5: Der E/A-Expander MIC74YQS-TR von Microchip Technology wandelt den seriellen Datenstrom in acht unabhängige parallele E/A-Leitungen um. (Bildquelle: Microchip Technology)

Dieser IC ist ein voll programmierbarer E/A-Expander mit acht unabhängigen E/A-Leitungen. Die E/A-Leitungen können individuell als Eingang oder als Ausgang programmiert werden. Abbildung 5 zeigt, wie das MIC74YQS-TR acht LEDs unter der Steuerung des seriellen Busses ansteuert. Dies ist vergleichbar mit der Verwendung des MCO23008 auf dem Demoboard I2C in Abbildung 1. Das MIC74YQS-TR kann in Verbindung mit einem Leistungsregler auch eine Lüftermotor-Drehzahlregelung unter Verwendung seiner vier wichtigsten Bits implementieren.

SMBus und I2C

Der serielle Eingang zum E/A-Expander ist für den SMBus ausgelegt, aber er ist auch mit dem I2C-Bus kompatibel. Die SMBus-Spezifikation basiert auf I2C und wurde 1994 von Intel und Duracell definiert. Der Hauptunterschied besteht darin, dass die logischen Ebenen des Standardmodus I2C relativ zu VDD und die des SMBus festgelegt sind. In den meisten Fällen mit VDD zwischen 3 Volt und 5 Volt, hat die Erfahrung gezeigt, dass dies kein Problem darstellt.

Ein weiterer Unterschied besteht darin, dass SMBus auf Taktraten von 100 kHz oder weniger beschränkt ist, während I2C über mehrere Modi verfügt, die höhere Taktraten unterstützen. Wenn es um Buskompatibilität geht, begrenzt dies die maximale Taktrate auf 100 kHz oder den Standardtaktmodus I2C.

Abgesehen von sehr speziellen Situationen sind also SMBus und I2C kompatibel.

Fazit

Der I2C-Bus und seine Ableitungen sind in Hunderten von ICs aller Typen weit verbreitet, so dass sie in vielfältigen Designs und Anwendungen leicht angeschlossen werden können. Die Kopplung von Mixed-Signal- und Analogsensoren erweitert den Anwendungsbereich von Mikrocontroller-basierten eingebetteten Systemen. All dies über eine einfache, serielle digitale Zweidraht-Schnittstelle.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.