Verwendung eines effizienten Multicore-Prozessors zur Erstellung intelligenter sprachaktivierter Produkte

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2020-02-14

Die Nachfrage nach intelligenteren Produkten ist in fast allen Anwendungsbereichen allgegenwärtig geworden, da die Benutzer mit virtuellen digitalen Assistenten wie Amazon Alexa, Google Assistant, Apple Siri und Microsoft Cortana vertraut sind und diese vertrauen. Neben der Bequemlichkeit spielen diese Assistenten eine wachsende Rolle bei der Verbesserung der Sicherheit und des Schutzes in einer breiten Palette von Produkten für industrielle Systeme und Anwendungen im Gesundheitswesen. Für die Entwickler bringen die diesen Produkten zugrunde liegenden Designs jedoch manchmal widersprüchliche Anforderungen an Prozessoren mit sich, die in der Lage sind, eine verbesserte Leistung, optimierte Kosten und Stellfläche sowie einen effizienten Betrieb zu liefern.

Dieser Artikel zeigt, wie Entwickler einen Multicore-Prozessor - in diesem Fall den i.MX 8M Nano von NXP - einsetzen können, um die breit gefächerten Verarbeitungs- und Schnittstellenanforderungen neuer intelligenter Produkte in Anwendungssegmenten zu erfüllen, die von intelligenter Haus- und Industrieautomatisierung bis hin zu medizinischen Systemen reichen. Dieser Artikel zeigt insbesondere, wie Entwickler diesen Prozessor nutzen können, um sprachbasierte Lösungen der nächsten Generation mit erweiterten Audioverarbeitungsfunktionen leichter zu implementieren.

Wie sich intelligente Produkte entwickeln

Der rasche Aufstieg von Sprachassistenten-Technologien hat dazu geführt, dass Benutzer nach mehr Funktionalität von intelligenten Produkten suchen. Neu aufkommende Produkte müssen nicht nur auf Sprachbefehle reagieren, sondern auch mehr Intelligenz einbinden, indem sie eine größere Vielfalt an Eingangsdaten von Sensoren, Kameras und anderen Produkten nutzen. Es reicht nicht aus, dass intelligente Lichtschalter das Licht ein- und ausschalten oder dass Geschirrspüler auf Sprachbefehle reagieren. Da die Anwendungen immer ausgereifter werden, müssen die ihnen zugrunde liegenden Geräte immer vielfältigere Kombinationen von Sensoren, erweiterte Verarbeitungsmöglichkeiten mit Methoden der künstlichen Intelligenz (KI) und 3D-Grafikanzeigen unterstützen.

Der Bedarf an intelligenteren Produkten geht über den Wunsch nach mehr Komfort hinaus. In kritischen Anwendungsbereichen wie der industriellen Automatisierung und dem Gesundheitswesen kann sich die Fähigkeit eines Geräts, seine Benutzer proaktiv auf Gefahren oder pathologische Zustände aufmerksam zu machen, als wesentlich erweisen. Ein Fabrikarbeiter, der einen Schutzhelm trägt, der die unmittelbare Umgebung überwachen kann, kann Gefahren leichter vermeiden; ein Risikopatient, der einen winzigen Gesundheitsmonitor trägt, der kontinuierlich die Lebenszeichen überwacht, kann lange vor einer Krise die erforderliche Intervention erhalten.

Diese und andere intelligente Produkte stellen spezifische Designanforderungen, die so unterschiedlich sind wie ihre Zielanwendungen, aber die meisten teilen den Bedarf an Hochleistungs-Verarbeitung, Multimedia-Fähigkeiten und sicherem Betrieb. Für die Entwickler verbinden sich diese funktionalen Anforderungen mit dem grundsätzlichen Bedarf an Lösungen, die in der Lage sind, für robustere Anwendungen zu skalieren und gleichzeitig physisch zu verkleinern, um den Erwartungen der Benutzer hinsichtlich reduzierter Größe, Kosten und Stromverbrauch gerecht zu werden. Die auf einer heterogenen Multicore-Architektur basierende NXP i.MX 8M Nano-Anwendungsprozessorfamilie erfüllt die breiten und vielfältigen Anforderungen an Designs für neue intelligente Produkte.

Leistungsfähige Kerne

Der NXP i.MX 8M Nano ist das neueste Mitglied der NXP i.MX 8M-Prozessorfamilie, die eine skalierbare Multicore-Verarbeitungsplattform bietet. Für High-End-Videoanwendungen bieten NXP i.MX 8M-Flaggschiffprozessoren wie der MIMX8MQ5DVAJZAB eine Anzeigeauflösung von bis zu 4K mit Hardware-Dekodierung von 4K-HDR-Video (High Dynamic Range). Für 1080p-Video bieten NXP i.MX 8M Mini-Prozessoren wie der MIMX8MM6CVTKZAA Unterstützung für 1080p-Hardware-Dekodierung. Sowohl die i.MX 8M- als auch die 8M-Mini-Serie kombinieren bis zu vier Arm® Cortex®-A53-Anwendungsprozessorkerne mit einem Arm Cortex-M4F-Mikrocontrollerkern.

Im Gegensatz dazu kombiniert der Prozessor NXP i.MX 8M Nano MIMX8MN6CVTIZAA vier Arm Cortex-A53-Kerne mit einem Arm Cortex-M7-Kern, der die höchste Leistung unter den anderen Kernen der Arm Cortex-M-Serie, einschließlich des Cortex-M4F, bietet.

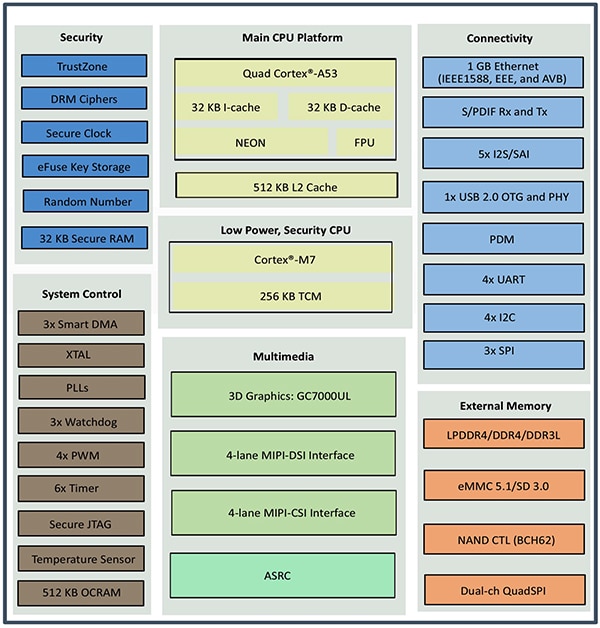

Neben ihrer Ergänzung durch Prozessorkerne unterstützen i.MX 8M Nano-Prozessoren eine Vielzahl von externen Speichergeräten und bieten eine vollständige Palette von externen Peripherieschnittstellen, die typischerweise in Verbraucher- und Industrieanwendungen benötigt werden (Abbildung 1).

Abbildung 1: Der NXP i.MX 8M Nano-Prozessor kombiniert bis zu vier Arm Cortex-A53-Anwendungsprozessoren, einen Arm Cortex-M7-Mikrocontroller, spezialisierte Hardware-Subsysteme und umfassende externe Peripherieschnittstellen, die typischerweise in Verbraucher- und Industrieanwendungen verwendet werden. (Bildquelle: NXP)

Abbildung 1: Der NXP i.MX 8M Nano-Prozessor kombiniert bis zu vier Arm Cortex-A53-Anwendungsprozessoren, einen Arm Cortex-M7-Mikrocontroller, spezialisierte Hardware-Subsysteme und umfassende externe Peripherieschnittstellen, die typischerweise in Verbraucher- und Industrieanwendungen verwendet werden. (Bildquelle: NXP)

Die verschiedenen verfügbaren Varianten der i.MX 8M Nano-Prozessorserie ermöglichen es Entwicklern, ihre spezifischen Anforderungen an Kosten und Leistung problemlos zu erfüllen. So integrieren die Hochleistungsmitglieder beispielsweise eine umfangreiche Palette spezialisierter Subsysteme für Sicherheit, 3D-Grafikanzeigen, Audioverarbeitung und mehr. Andere Mitglieder der i.MX 8M Nano-Serie bieten Optionen mit weniger Cortex-A53-Kernen und "Lite"-Versionen mit reduzierten Grafikfähigkeiten.

Alle Mitglieder der i.MX 8M Nano-Prozessorserie bieten dennoch die Fähigkeit, die Kombination aus Anwendungsleistung und Echtzeitfähigkeit zu liefern, die in neu entstehenden intelligenten Produkten benötigt wird.

Jeder Anwendungsprozessorkern des Arm Cortex-A53 wurde für die leistungsstarke Ausführung von Anwendungssoftware entwickelt und kann mit Taktfrequenzen von bis zu 1,5 Gigahertz (GHz) arbeiten, während er von einem dedizierten 32-Kilobyte (Kbyte)-Instruktions-Cache (I-Cache) der Ebene 1 (L1), einem 32-Kbyte-Daten-Cache (D-Cache) und einem gemeinsam genutzten einheitlichen L2 512-Kbyte-Cache arbeitet. Zusammen mit ihrer integrierten Gleitkommaeinheit (FPU) unterstützen diese Kerne die Neon-Technologie von Arm's Neon für erweiterte SIMD-Operationen (Single Instruction Multiple Data), die in der digitalen Signalverarbeitung und anderen fortschrittlichen Algorithmen in datenintensiven Anwendungen verwendet werden.

Für die Anforderungen eingebetteter Systeme läuft der Arm Cortex-M7-Mikrocontroller-Kern bei Frequenzen von bis zu 750 Megahertz (MHz) und bietet gleichzeitig eine hohe Leistung bei der Ausführung von Echtzeitprozessen, die eine geringe Latenzzeit und einen deterministischen Betrieb erfordern. Um die Verarbeitung weiter zu beschleunigen, umfasst der Kern eine integrierte FPU und 256 KByte eng gekoppelten Speicher (TCM), der für den Befehls- und Daten-Cache verwendet wird.

Bei komplexen Echtzeit-Verarbeitungsaufgaben kann jedoch die Fähigkeit zur schnellen Erkennung separater Unterbrechungsquellen ebenso entscheidend sein wie die Leistung der Rohdatenverarbeitung. In den i.MX 8M Nano-Prozessoren ermöglichen ein globaler Interrupt-Controller (GIC), der in jedem Arm Cortex-A53-Kern eingebaut ist, und ein verschachtelter Vektor-Interrupt-Controller (NVIC) im Arm Cortex-M7-Kern die Feinkorn-Interrupt-Behandlung von fast 128 verschiedenen Interrupt-Anforderungsquellen, die den Kernzuständen, Zeitgebern, peripheren Schnittstellenereignissen, DMA-Operationen (Direct-Memory-Access), spezialisierten Hardware-Prozessen und vielen anderen entsprechen.

Heterogene Mehrkernverarbeitung

Jeder einzelne i.MX 8M Nano-Prozessorkern bietet eine robuste Rechenleistung. Die mehreren Kerne des Prozessors bieten zusammen eine Hochleistungs-Computerplattform, die in der Lage ist, die widersprüchlichen Anforderungen an die Echtzeitleistung und die Ausführung von Anwendungssoftware zu bewältigen, die das Design intelligenter Produkte verwirren können. Ein intelligentes Produkt, das auf diesem Prozessor basiert, kann zum Beispiel den Cortex-M7-Kern zur Verarbeitung von Audioströmen in Echtzeit verwenden, während Algorithmen, die auf einem oder mehreren Cortex-A53-Kernen laufen, die resultierenden Daten analysieren und den Benutzern eine 3D-Grafikanzeige der Ergebnisse bieten.

Um diese Art von koordinierter heterogener Mehrkernverarbeitung zuverlässig durchzuführen, erfordert ein Mehrkernsystem jedoch eine sorgfältige Orchestrierung der Verarbeitungsvorgänge und des Datenaustauschs zwischen den verschiedenen Kernen, spezialisierten Hardwareblöcken und Peripheriegeräten. Im i.MX 8M Nano-Prozessor ist diese Orchestrierung in hardwarebasierte Mechanismen für Semaphoren und Messaging integriert, die typischerweise von Low-Level-Softwarediensten in Multiprozess-Umgebungen verwendet werden.

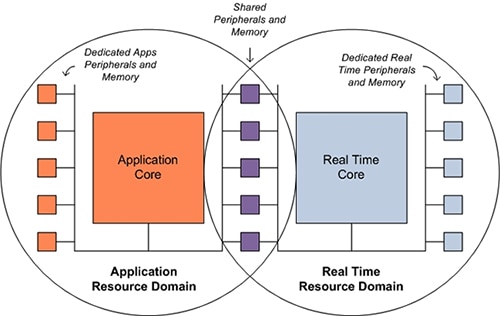

Bei eingebetteten Systemen erstreckt sich diese orchestrierte Ausführung auch auf Hardwareressourcen wie Speicher und Peripheriegeräte. Für diese Aufgabe integriert der Prozessor einen dedizierten Ressourcendomänen-Controller (RDC), der so konzipiert ist, dass eine sichere gemeinsame Nutzung von Ressourcen, wo dies angebracht ist, oder eine zuverlässige Isolierung, wenn dies erforderlich ist, gewährleistet ist. Als Ergebnis können Anwendungssoftware und Echtzeitcode jeweils die für ihre Domäne bestimmten Ressourcen steuern und gleichzeitig einen Satz gemeinsamer Ressourcen gemeinsam nutzen (Abbildung 2).

Abbildung 2: Hardware-basierte Mechanismen im NXP i.MX 8M Nano-Prozessor gewährleisten die Isolierung von Ressourcen, die der Cortex-A53-Anwendungsdomäne oder der Cortex-M7-Echtzeitdomäne zugeordnet sind, und ermöglichen gleichzeitig eine sichere gemeinsame Nutzung von Ressourcen, wo dies erforderlich ist. (Bildquelle: NXP)

Abbildung 2: Hardware-basierte Mechanismen im NXP i.MX 8M Nano-Prozessor gewährleisten die Isolierung von Ressourcen, die der Cortex-A53-Anwendungsdomäne oder der Cortex-M7-Echtzeitdomäne zugeordnet sind, und ermöglichen gleichzeitig eine sichere gemeinsame Nutzung von Ressourcen, wo dies erforderlich ist. (Bildquelle: NXP)

Spezialisierte Unterstützung für intelligente Produkte

Nur durch die Verwendung der mehreren Kerne und die gemeinsame Nutzung von Ressourcen des i.MX 8M Nano-Prozessors können Entwickler anspruchsvolle Anwendungen für neue intelligente Produkte mit Sprachassistenten und 3D-Grafik erstellen. Diese Anwendungen erhalten eine weitere Leistungssteigerung und reduzieren gleichzeitig ihren Software-Fußabdruck dank der speziellen Hardware-Unterstützung für intelligente Produkte, die in i.MX 8M Nano-Prozessoren eingebaut sind.

Für die Grafik bietet die integrierte Grafikverarbeitungseinheit (GPU) des Prozessors 2D- und 3D-Grafikbeschleunigung und unterstützt Standardgrafikbibliotheken wie Vulkan, Open Computing Language (OpenCL) und Open Graphics Library (OpenGL). Ein integrierter LCDIF-Controller (Liquid Crystal Display Interface) unterstützt Anzeigen mit 1080p60 (1080 progressive 60 Bilder pro Sekunde).

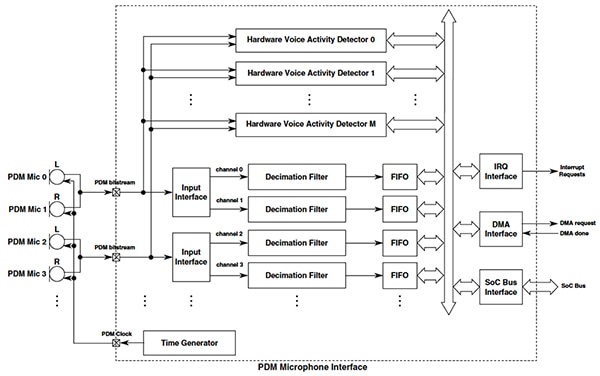

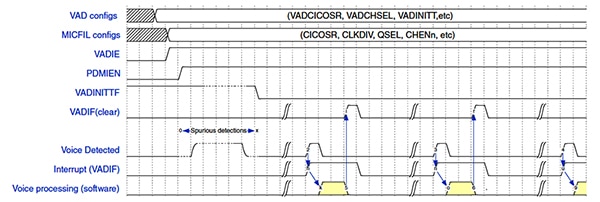

Während die On-Chip-GPU die Anzeigeverarbeitung von den Kernen entlastet, entlastet ein anderer Satz von Hardware-Subsystemen eine Vielzahl von Audioverarbeitungsaufgaben, die normalerweise bei Systemen mit herkömmlichen Prozessoren langsam sind. Für die Verarbeitung von Mikrofoneingaben bietet die PDM-Mikrofonschnittstelle (MICFIL) des Prozessors eine mehrstufige Pipeline, die so konzipiert ist, dass sie gefilterte 16-Bit-PCM-Daten (PCM = Pulse Code Modulation) aus den von PDM-Mikrofonen empfangenen 1-Bit-Eingaben erzeugt (Abbildung 3).

Abbildung 3: Das Schnittstellensubsystem des NXP i.MX 8M Nano-Prozessors für den PDM-Mikrofoneingang kombiniert separate Hardware-Pipelines für die Audiosignalverarbeitung und die Erkennung von Sprachaktivitäten. (Bildquelle: NXP)

Abbildung 3: Das Schnittstellensubsystem des NXP i.MX 8M Nano-Prozessors für den PDM-Mikrofoneingang kombiniert separate Hardware-Pipelines für die Audiosignalverarbeitung und die Erkennung von Sprachaktivitäten. (Bildquelle: NXP)

Für eine typische sprachbasierte Anwendung müssen Designer lediglich ein PDM-Mikrofon an einen der acht vom Prozessor unterstützten PDM-Kanäle anschließen. Innerhalb des PDM-Mikrofonschnittstellensubsystems kombiniert eine Eingangsschnittstelle zeitmultiplexe PDM-Daten von einem Mikrofonpaar, um eine Spur zu bilden, die den linken und rechten Kanal umfasst.

In der nächsten Stufe bietet ein spezieller programmierbarer Dezimationsfilter für jeden Kanal unterschiedliche Durchlassbereiche, je nach der gewünschten Ausgaberate und einer von sechs Qualitätseinstellungen (QSEL), darunter hohe, mittlere und niedrige Qualität, sowie drei zusätzliche sehr niedrige Qualitätsstufen. Bei einer Ausgangsrate von 48 Kilohertz (kHz) wird beispielsweise bei den Modi mit sehr geringer Qualität der Filterdurchlassbereich auf 10,5 Hz bis 11,25 kHz eingestellt, im Vergleich zu einem Durchlassbereich von 21 Hz bis 22,5 kHz für die Modi mit hoher, mittlerer und geringer Qualität. Schließlich werden die Ergebnisse für jeden Kanal in separaten FIFO-Puffern (first-in, first-out) für jeden Kanal zur Erzeugung von Interrupts, zur Übertragung mittels DMA oder zum Buszugriff bereitgestellt.

Hardware-basierte Sprachaktivitätserkennung

Parallel zu dieser Audiosignalkonditionierungs-Pipeline bietet die PDM-Mikrofonschnittstelle eine Reihe von Hardware-Sprachaktivitätsdetektoren (HWVADs), die die gewünschten Mikrofoneingangskanäle überwachen. (Hinweis: Die obige Abbildung zeigt, dass jedes HWVAD mit einer Fahrspur verbunden ist, aber in der Dokumentation steht Kanäle, und der Name eines Registers, VADCHSEL, unterstützt dies). Zur Unterstützung des HWVAD-Betriebs stellt der Prozessor einen umfangreichen Satz von Geräteregistern zur Verfügung, die es Entwicklern ermöglichen, die für ihre Anwendung erforderliche spezifische HWVAD-Konfiguration zu definieren (Tabelle 1).

|

Tabelle 1: NXP i.MX 8M Nano-Prozessorregister, die normalerweise zur Konfiguration der in die PDM-Mikrofonschnittstelle des Prozessors integrierten Hardware-Sprachaktivitätsdetektoren (MICFIL) verwendet werden. (Tabellenquelle: DigiKey, basierend auf NXP-Daten)

Auf der Grundlage dieser Registereinstellungen verwendet der HWVAD integrierte Spracherkennungsalgorithmen zur Identifizierung von Sprachaktivitäten. Bei der Erkennung erzeugt der HWVAD eine Unterbrechung, um einen Kern, typischerweise den Cortex-M7, zur weiteren Verarbeitung aufzuwecken (Abbildung 4).

Abbildung 4: Mit Hilfe von Konfigurationseinstellungen, die vom Entwickler programmiert wurden, ermöglichen die Sprachaktivitätsdetektoren der NXP i.MX 8M Nano-Prozessor-Hardware den Prozessorkernen, in den Ruhezustand zu gehen oder andere Verarbeitungen durchzuführen, bis eine Stimme erkannt wird und eine weitere Sprachverarbeitung erforderlich ist. (Bildquelle: NXP)

Abbildung 4: Mit Hilfe von Konfigurationseinstellungen, die vom Entwickler programmiert wurden, ermöglichen die Sprachaktivitätsdetektoren der NXP i.MX 8M Nano-Prozessor-Hardware den Prozessorkernen, in den Ruhezustand zu gehen oder andere Verarbeitungen durchzuführen, bis eine Stimme erkannt wird und eine weitere Sprachverarbeitung erforderlich ist. (Bildquelle: NXP)

In einer Sprachassistenten-Anwendung würde der Kern den Audiostrom auf das entsprechende Wake-Wort überprüfen. Wenn das Wake-Word erkannt wird, stellt der Kern normalerweise den Audiostrom für die von der Anwendung unterstützten wolkenbasierten Sprachassistentendienste bereit.

Neben dem PDM-Mikrofon-Schnittstellensubsystem bietet der i.MX 8M Nano-Prozessor auch fünf SAI-Module (Synchronous Audio Interface), die eine Reihe von Standard-Audioformaten unterstützen, darunter Inter-IC Sound (I2S), Audiocodec 97 (AC97), Zeitmultiplex-Audio (TDM) und Direct Stream Digital (DSD) sowie Codec- oder DSP-Daten (Digital Signal Processing).

Um ihren spezifischen Anwendungsanforderungen gerecht zu werden, müssen Entwickler oft die Aufgabe haben, die Audio-Eingangssamples in eine andere erforderliche Abtastrate und Auflösung zu konvertieren. Anstatt Prozessorzyklen zur Bewältigung dieser gemeinsamen Aufgabe zu verwenden, integriert der i.MX 8M Nano-Prozessor ein dediziertes asynchrones Abtastratenwandler-Subsystem (ASRC).

Der ASRC kann bis zu 32 Audiokanäle gleichzeitig verarbeiten und wandelt die Quell-Samples automatisch in die gewünschte Abtastrate (zwischen 8 kHz und 384 kHz) und Auflösung (IEEE Single-Precision-Fließkomma- oder Festkomma-Format mit 16, 20, 24 oder 32 Bit pro Sample) um. Dabei wandelt der ASRC alle Eingangsdaten in ein 64-Bit-IEEE-Fließkommaformat um, um eine genaue Auf- oder Abwärtskonvertierung der Audio-Sample-Daten zu gewährleisten, die für das gewünschte Ergebnis erforderlich ist.

Leistungsmanagement mit einem allgemeinen Leistungsregler

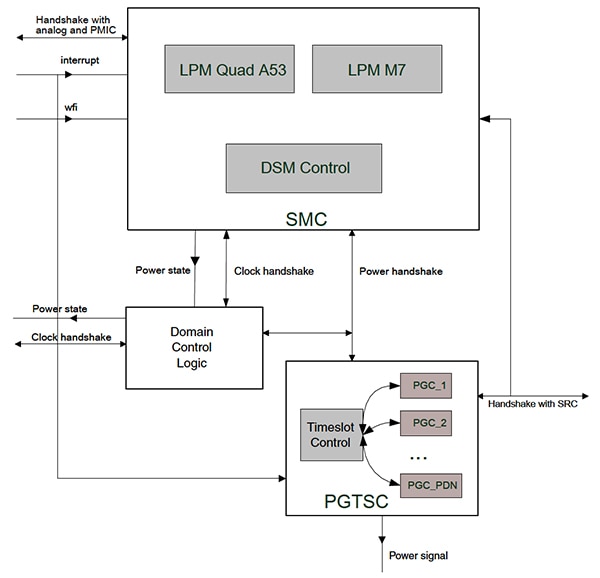

Durch die umfassende Integration von Prozessorkernen und Hardware-Subsystemen kombiniert die NXP i.MX 8M Nano-Prozessorarchitektur eine Reihe von separaten Leistungsbereichen und Leistungsmodi, die in die einzelnen Kerne und Subsysteme eingebaut sind. Um die Leistung für diese Sammlung von Kernen und spezialisierten Blöcken zu verwalten, enthält der i.MX 8M Nano-Prozessor einen hochentwickelten allgemeinen Leistungsregler (GPC), der für die Koordinierung mehrerer Leistungsmanagement-Funktionen ausgelegt ist. Innerhalb des GPC verwaltet der System Mode Controller (SMC) den Low-Power-Modus (LPM) und den gesamten Tiefschlaf-Modus (DSM) jedes Kerns, während ein Power Gating Time Slot Controller (PGTSC) die Taktgeberfunktionen verwaltet, die zur Reduzierung der Systemleistung durch Abschalten der Leistung zu inaktiven Subsystemen verwendet werden (Abbildung 5).

Abbildung 5: Um die Leistungsoptimierung auf Systemebene zu verbessern, integriert der NXP i.MX 8M Nano einen umfassenden Leistungsregler, der die in den Prozessorkernen eingebauten Power-Gate-Funktionen und Low-Power-Modi verwaltet. (Bildquelle: NXP)

Abbildung 5: Um die Leistungsoptimierung auf Systemebene zu verbessern, integriert der NXP i.MX 8M Nano einen umfassenden Leistungsregler, der die in den Prozessorkernen eingebauten Power-Gate-Funktionen und Low-Power-Modi verwaltet. (Bildquelle: NXP)

Sowohl software- als auch hardwaregesteuert verwendet der GPC 20 verschiedene Zeitschlitze im PGTSC, um eine der mehreren taktgesteuerten Leistungsdomänen im Prozessor ein- oder auszuschalten. Hier arbeitet der Zeitschlitz-Controller diese Zeitschlitze sequentiell ab und aktiviert alle Ein- und Ausschaltanforderungen, bevor er zum nächsten Schlitz weitergeht. Neben der Erfüllung spezifischer Anforderungen an die Leistungssequenzierung ermöglicht dieser Ansatz den Entwicklern, den Anlaufstrom während des Einschaltens des Systems oder beim Aufwecken des Systems aus einem Niedrigleistungs- oder Tiefschlafmodus zu reduzieren.

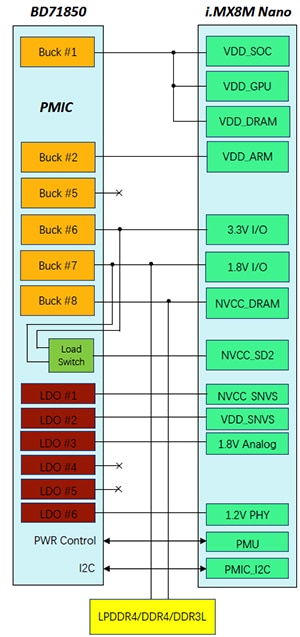

Die Versorgung der verschiedenen Leistungsbereiche des i.MX 8M Nano-Prozessors ist unkompliziert. Der speziell zur Unterstützung des NXP i.MX 8M Nano-Prozessors entwickelte integrierte Power-Management-Circuit (PMIC) von ROHM Semiconductor BD71850MWV bietet alle vom Prozessor benötigten Stromschienen sowie andere Systemperipheriegeräte. Tatsächlich integriert der BD71850MWV PMIC seinen eigenen Power-Sequenzer, was die sichere Ausführung des Ein- und Ausschaltens nicht nur für den Prozessor, sondern auch für externe Speicher, Sensoren oder andere Geräte im System weiter vereinfacht (Abbildung 6). Für Entwickler erfordert die Integration des BD71850MWV-PMIC in ein Design keine zusätzlichen Komponenten über die üblichen Entkopplungskondensatoren hinaus (nicht abgebildet).

Abbildung 6: Der NXP iMX 8M Nano-Prozessor mit mehreren Kernen und Hardware-Subsystemen erfordert mehrere Versorgungsschienen, aber der integrierte Strommanagementschaltkreis (PMIC) ROHM BD71850MWV bietet eine fertige Lösung. (Bildquelle: NXP)

Abbildung 6: Der NXP iMX 8M Nano-Prozessor mit mehreren Kernen und Hardware-Subsystemen erfordert mehrere Versorgungsschienen, aber der integrierte Strommanagementschaltkreis (PMIC) ROHM BD71850MWV bietet eine fertige Lösung. (Bildquelle: NXP)

Entwicklungsunterstützung

Obwohl die Anforderungen an die Hardwareschnittstelle für i.MX 8M Nano-basierte Designs relativ einfach sind, können Entwickler mit NXP selbst diese relativ einfache Designaufgabe für die Evaluierung des Prozessors oder das Prototyping neuer intelligenter Produkte vermeiden. Das 8MNANOD4-EVK-Evaluierungskit bietet ein vollständig implementiertes Entwicklungskit und ein Referenzdesign für den i.MX 8M Nano-Prozessor. Es kombiniert den i.MX 8M Nano-Prozessor und den BD71850MWV-PMIC mit dem Murata Electronics LBEE5HY1MW Wi-Fi/Bluetooth-Transceivermodul und bietet so eine Plattform für die sofortige Evaluierung und die Entwicklung von Prototypen. Neben mehreren Schnittstellenoptionen und zugehörigen Anschlüssen enthält das Evaluationskit einen vollständigen Satz externer Speicherbausteine, einschließlich statisch-dynamischer Speicher (SDRAM), NOR-Flash und NAND-Flash. Mit dem Evaluation-Kit können Entwickler verschiedene Betriebsmodi und Konfigurationen untersuchen, einschließlich des Bootens von externem Flash oder des sicheren Bootens mit signierten Boot-Images.

Wenn Entwickler bereit sind, mit ihrer eigenen kundenspezifischen Softwareentwicklung fortzufahren, stellt NXP Treiber, Board Support Packages (BSPs) und Middleware zur Verfügung, die für die Arbeit mit der eigenen integrierten Entwicklungsumgebung (IDE) MCUXpresso sowie IDEs von Drittanbietern konzipiert sind. Für die Erstellung von Anwendungen, die auf die Nutzung von maschinellen Lernmethoden ausgerichtet sind, können Entwickler auf die NXP eIQ-Softwareentwicklungsumgebung für maschinelles Lernen und i.MX-optimierte Inferenzbibliotheken zurückgreifen, wie z.B. eIQ für TensorFlow Lite für Cortex-M7-basierte Inferenz oder NXPs Portierung des Arm Neural Network Software Development Kit (NN SDK) für Cortex-A53-basierte Inferenz.

Fazit

Angetrieben durch die rasche Akzeptanz von Sprachassistentenprodukten sehen sich die intelligenten Produkte der nächsten Generation wachsenden Erwartungen gegenüber, die nicht nur eine bessere Audiounterstützung, sondern auch eine höhere Leistung, verbesserte Grafik und einen energieeffizienten Betrieb erwarten. Für Entwickler erfordert ein effektives Systemdesign für diese Produkte jedoch eine Kombination aus hochleistungsfähiger Anwendungssoftware und Echtzeitfähigkeiten mit geringer Latenz, die im Rahmen der damit verbundenen Größen-, Kosten- und Leistungsbeschränkungen bisher nur schwer zu erreichen war. Mit der Verfügbarkeit einer skalierbaren Familie von Multicore-Prozessoren von NXP können Entwickler die Design-Anforderungen für intelligente Produkte in einer Vielzahl von Anwendungssegmenten, u. a. in den Bereichen Konsumgüter, Industrie und Medizin, problemlos erfüllen.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.