Schnelles Erzeugen von Hochfrequenztakten mit geringem Jitter mit einem Translationsschleifenmodul

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2021-08-04

Entwickler von Instrumenten- und Messsystemen benötigen störungsfreie Signale mit geringem Jitter, um die Signal-Rausch-Verhältnisse (SNRs) oder Fehlervektoren (EVMs) bereitzustellen, die für die Erfüllung der immer anspruchsvolleren Kundenanforderungen erforderlich sind. Gleichzeitig stehen sie unter erheblichem Druck, den Platzbedarf auf der Leiterplatte, die Entwicklungskosten und die Komplexität zu reduzieren. Letzteres ist von entscheidender Bedeutung, um die Entwicklungszeit zu verkürzen und die immer enger werdenden Zeitfenster bis zur Markteinführung einzuhalten.

Um den zahlreichen Anwendungsherausforderungen gerecht zu werden, müssen die Ingenieure ihre Instrumenten- und Messtaktungslösungen von traditionell diskreten Sonderanfertigungen auf stärker integrierte Lösungen umstellen. Ein wichtiger Schritt in diese Richtung ist die Verwendung einer integrierten Translations-Phasenregelschleife (PLL). Dies ermöglicht die Frequenzaufwärtskonvertierung eines herkömmlichen spannungsgesteuerten Oszillatorsignals (VCO), während der Jitter und das Phasenrauschen eines festen externen lokalen Oszillators (LO) im Wesentlichen erhalten bleiben.

In diesem Artikel wird die Rolle von Translationsschleifen beim Erreichen des branchenweit niedrigsten integrierten Phasenrauschens erörtert. Als Beispiel wird das TL-SiP (Translation-Loop-System-in-Package) ADF4401A von Analog Devices vorgestellt und gezeigt, wie es die Leistungsanforderungen durch ein Ausgangssignal mit einem integrierten effektiven Breitband-Jitter von unter 10 Femtosekunden (fs) und einer verbesserten Isolierung zur Dämpfung von Störkomponenten erfüllt und gleichzeitig die Anforderungen der Entwickler in Bezug auf Integration, Kosten, Komplexität und Markteinführungszeit erfüllt.

Traditioneller PLL vs. Translationsschleifenbetrieb

Der Hauptzweck einer Translationsschleife besteht darin, ein Ausgangssignal zu erzeugen, das an ein Eingangsreferenzsignal gekoppelt ist und im Vergleich zu herkömmlichen PLLs ein deutlich geringeres In-Band-Phasenrauschen aufweist.

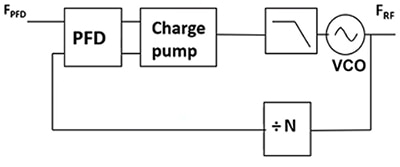

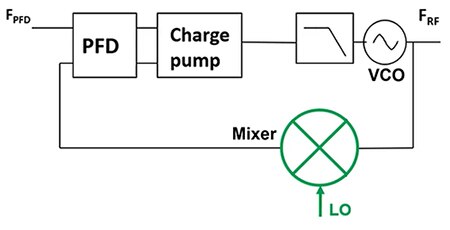

Eine Standard-PLL besteht aus einem Rückkopplungssystem mit einem Phasenfrequenzdetektor (PFD), einer Ladungspumpe, einem Tiefpassfilter (LPF), einem VCO und einem Rückkopplungsfrequenzteiler N (Abbildung 1).

Abbildung 1: Die Standard-PLL koppelt sich an eine niedrigere Referenzfrequenz (FPFD) und erzeugt eine Ausgangsfrequenz (FRF). (Bildquelle: Bonnie Baker)

Abbildung 1: Die Standard-PLL koppelt sich an eine niedrigere Referenzfrequenz (FPFD) und erzeugt eine Ausgangsfrequenz (FRF). (Bildquelle: Bonnie Baker)

Der PFD vergleicht die Phase des Eingangssollwerts mit der Phase des Rückkopplungssignals und erzeugt eine Reihe von Impulsen, die proportional zum Phasenfehler zwischen ihnen sind. Die Ladungspumpe empfängt die PFD-Impulse und wandelt sie in Stromquellen- bzw. Stromsenkenimpulse um, die wiederum den VCO entweder in der Frequenz nach oben oder unten abstimmen. Der LPF entzieht den Impulsen die gesamte Hochfrequenzenergie und wandelt sie in eine Spannung um, die der VCO nutzen kann. Das Ausgangssignal des VCO wird über den N-Teiler in den PFD-Block zurückgeführt, um die Schleife zu schließen.

Die Frequenzübertragungsfunktion von Abbildung 1 wird mit Gleichung 1 berechnet:

![]() Gleichung 1

Gleichung 1

Dabei ist FRF die Ausgangsfrequenz

N ist das Verhältnis des Rückkopplungsteilers (kann ganzzahlig oder gebrochen sein)

FPFD ist die PFD-Frequenz

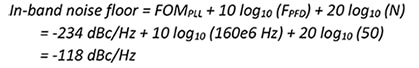

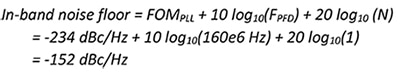

Das bandinterne Grundrauschen von Abbildung 1 wird mit Gleichung 2 berechnet:

![]() Gleichung 2

Gleichung 2

Dabei ist FOMPLL die Gütezahl des In-Band-Phasengrundrauschens (FOM) der PLL

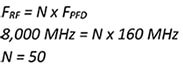

Nehmen wir ein Beispiel mit einer FOM von -234 Dezibel pro Hertz (dB/Hz) für das In-Band-Phasengrundrauschen, einer PFD-Frequenz (FPFD) von 160 Megahertz (MHz) und einer Ausgangsfrequenz (FRF) von 8 Gigahertz (GHz).

Für dieses System wird Gleichung 1 verwendet, um den Wert von N zu berechnen:

Gleichung 2 dient zur Berechnung des Grundrauschens im Band:

In der obigen Berechnung trägt der N-Teiler mit 20 log10 (50), d. h. 34 dB, stark zum gesamten bandinternen Rauschpegel bei. Ein kleinerer N-Wert würde das bandinterne Grundrauschen verringern, aber auch die Ausgangsfrequenz senken. Wie können wir also eine hohe Ausgangsfrequenz erzeugen und eine niedrige Schleifenverstärkung (N) beibehalten?

Abbildung 2: Bei einer Standard-PLL in diesem Beispiel hat das Rauschen des Rückkopplungsteilers (20 log10(N)) ein um 34 dB höheres bandinternes Rauschen im Vergleich zum unteren gelben Diagramm mit N = 1. (Bildquelle: Bonnie Baker)

Abbildung 2: Bei einer Standard-PLL in diesem Beispiel hat das Rauschen des Rückkopplungsteilers (20 log10(N)) ein um 34 dB höheres bandinternes Rauschen im Vergleich zum unteren gelben Diagramm mit N = 1. (Bildquelle: Bonnie Baker)

Die Lösung für dieses Problem besteht darin, den N-Teiler durch eine abwärtswandelnde Mischstufe zu ersetzen (Abbildung 3).

Abbildung 3: Eine Translationsschleife verwendet einen Mischer, um die VCO-Frequenz auf die PFD-Frequenz herunterzuwandeln, anstatt einen herkömmlichen Rückkopplungsteiler zu verwenden. (Bildquelle: Bonnie Baker)

Abbildung 3: Eine Translationsschleife verwendet einen Mischer, um die VCO-Frequenz auf die PFD-Frequenz herunterzuwandeln, anstatt einen herkömmlichen Rückkopplungsteiler zu verwenden. (Bildquelle: Bonnie Baker)

In Abbildung 3 ersetzt der Mischer den rückgekoppelten N-Teiler, was zu einer Schleifenverstärkung von 1 (N=1) führt. Dadurch wird der Beitrag der Rückkopplungsschleife zum Grundrauschen im Frequenzbereich erheblich verringert. Für die Berechnung des In-Band-Rauschens ist der Wert von N nun gleich 1. Unter Verwendung von Gleichung 2 ergibt sich für das geänderte System das Grundrauschen im Frequenzband wie folgt:

Das neue bandinterne Rauschen weist eine Verbesserung von 34 dBc/Hz auf.

In Abbildung 3 hängt der Mischer von einem extrem rauscharmen LO ab, dem so genannten Offset-LO. FLO ± FRF muss gleich FPFD sein, um eine Kopplung zu erreichen.

Bei der Architektur der Translationsschleife ist das Phasenrauschen des Offset-LO sehr wichtig, um die beste Leistung am HF-Ausgang zu erzielen. Aus diesem Grund entwerfen Ingenieure in der Regel einen Offset-LO auf der Grundlage von spannungsgesteuerten akustischen Oberflächenwellen (SAW), Oszillatoren (VCSOs), Kammgeneratoren oder dielektrischen Resonatoroszillatoren (DROs). HINWEIS: Für Unterstützung bei der Entwicklung eines Offset-LOs wenden Sie sich bitte an Analog Devices.

Herausforderungen bei der Translationsschleife

Der Entwurf einer rauscharmen Translationsschleife erfordert in der Regel die Implementierung zahlreicher Schaltungsblöcke, was zu einem komplexen, in der Regel großen Entwurf mit begrenzter Flexibilität führt. Darüber hinaus muss die gesamte Schaltung für den angestrebten Betrieb validiert und charakterisiert werden. Ein großes Problem bei der Entwicklung ist zum Beispiel der LO-Verlust (LO-HF-Isolation) zum HF-Ausgangssignal. Dies ist eine große Herausforderung für die Ingenieure, die es zu bewältigen gilt. Bei herkömmlichen Entwürfen führen die Ingenieure in der Regel mehrere Entwurfsiterationen durch, um eine optimale Leistung und eine geeignete Isolierung zu erreichen.

Abbildung 3 zeigt, wie der ADF4401A wichtige Schaltungsblöcke integriert, um eine vollständig charakterisierte Lösung zu bieten und die traditionell schwierigen Bereiche im Zusammenhang mit der Leistung und Isolierung in Translationsschleifendesigns zu eliminieren. Diese programmierbare Lösung ermöglicht es den Ingenieuren, gleich beim ersten Versuch eine optimale Leistung zu erzielen und die Markteinführungszeit zu verkürzen.

Evaluierung des ADF4401A

Der ADF4401A wurde entwickelt, um Ingenieuren zu helfen, die Zeit bis zur Markteinführung von Hochleistungsinstrumenten zu verkürzen, indem er eine Frequenzgenerierungslösung mit einer HF-Bandbreite von 62,5 MHz bis 8 GHz verwendet. Durch die Verwendung eines abwärtswandelnden Mischers hat der ADF4401A ein sehr geringes In-Band-Rauschen mit einem Breitband-Jitter von ~9 Femtosekunden (fs) integriert von 100 Hz bis 100 MHz. Die Design- und Layouttechniken des ADF4401A ermöglichen einen typischen störungsfreien Dynamikbereich von 90 dBc. Mit einer Gehäusegröße von 18 x 18 x 2,018 Millimetern (mm) wird der Platz auf der Leiterplatte im Vergleich zu einem herkömmlichen diskreten Design erheblich reduziert.

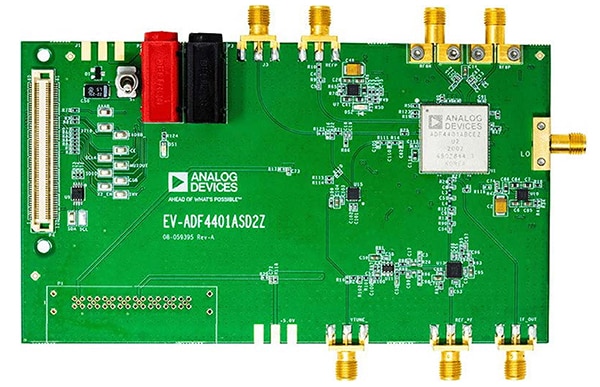

Um die Leistung des Bausteins zu evaluieren, können Entwickler das Evaluierungsboard EV-ADF4401ASD2Z verwenden (Abbildung 4). Das Board enthält eine komplette Translationsschleife, einschließlich eines externen PFD (HMC3716), eines aktiven Filters (LT6200) und eines Multiplexers (ADG1609).

Abbildung 4: Das Evaluierungsboard EV-ADF4401ASD2Z für das Translationsschleifenmodul ADF4401A enthält einen externen PFD, eine USB-Schnittstelle und Spannungsregler. (Bildquelle: Analog Devices)

Abbildung 4: Das Evaluierungsboard EV-ADF4401ASD2Z für das Translationsschleifenmodul ADF4401A enthält einen externen PFD, eine USB-Schnittstelle und Spannungsregler. (Bildquelle: Analog Devices)

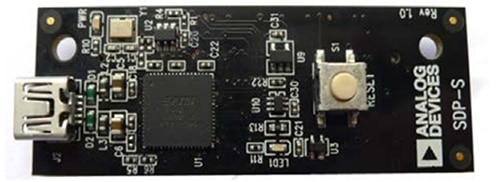

Das EV-ADF4401ASD2Z enthält den TL-SiP ADF4401A mit integriertem VCO, einem Schleifenfilter (5 MHz), einem PFD, einer USB-Schnittstelle und Spannungsreglern. Zusätzlich benötigt das EV-ADF4401ASD2Z die serielle SDP-S-Controllerkarte EVAL-SDP-CS1Z (SDP-S: System Demonstration Platform (Serial)) (Abbildung 5). Die Karte bietet eine USB-Verbindung zwischen einem PC und dem EV-ADF4401ASD2Z, so dass es programmiert werden kann. Die Steuerkarte ist nicht im Lieferumfang des EV-ADF4401ASD2Z-Kits enthalten.

Abbildung 5: Die Controllerkarte EVAL-SDP-CS1Z (oder SDP-S) wird benötigt, um eine USB-Verbindung zwischen dem EV-ADF4401ASD2Z und einem PC zur Programmierung herzustellen. (Bildquelle: Analog Devices)

Abbildung 5: Die Controllerkarte EVAL-SDP-CS1Z (oder SDP-S) wird benötigt, um eine USB-Verbindung zwischen dem EV-ADF4401ASD2Z und einem PC zur Programmierung herzustellen. (Bildquelle: Analog Devices)

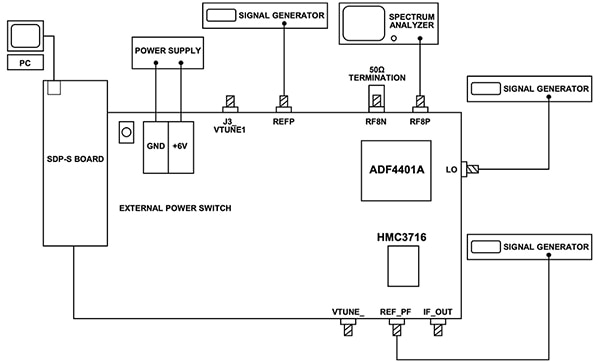

In Abbildung 6 sind die physikalischen Anschlüsse des EV-ADF4401ASD2Z-Systems dargestellt. Die zugehörige ACE-Software (Analyse | Steuerung | Evaluierung) steuert die Funktionen des TL-SiP. Die Stromversorgung erfolgt über ein externes 6-Volt-Netzteil.

Abbildung 6: Dieses Anschlussdiagramm für das EV-ADF4401ASD2Z zeigt die Geräte und Anschlüsse, die zur Evaluierung des ADF4401A erforderlich sind, einschließlich der SDP-S-Steuerplatine, des PCs, der Stromversorgung, der Signalgeneratoren und des Spektrumanalysators. (Bildquelle: Analog Devices)

Abbildung 6: Dieses Anschlussdiagramm für das EV-ADF4401ASD2Z zeigt die Geräte und Anschlüsse, die zur Evaluierung des ADF4401A erforderlich sind, einschließlich der SDP-S-Steuerplatine, des PCs, der Stromversorgung, der Signalgeneratoren und des Spektrumanalysators. (Bildquelle: Analog Devices)

Zu den empfohlenen Geräten für diese Evaluierungskarte gehören ein Windows-PC, ein Spektrumanalysator oder ein Signalquellenanalysator und drei Signalgeneratoren.

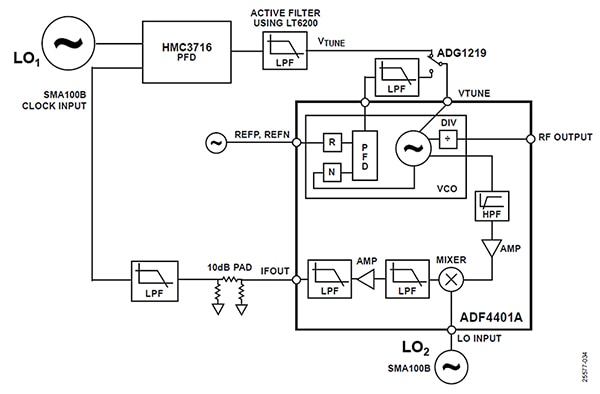

Das Blockdiagramm des EV-ADF4401ASD2Z zeigt das ADF4401A-Modul zusammen mit dem PFD HMC3716 von Analog Devices, dem Operationsverstärker LT6200 und dem SPDT-Schalter ADG1219 (Abbildung 7).

Abbildung 7: Das Blockdiagramm der Evaluierungsplatine EV-ADF4401ASD2Z zeigt die Hauptkomponenten, die die Translationsschleife AD4401A unterstützen. (Bildquelle: Analog Devices)

Abbildung 7: Das Blockdiagramm der Evaluierungsplatine EV-ADF4401ASD2Z zeigt die Hauptkomponenten, die die Translationsschleife AD4401A unterstützen. (Bildquelle: Analog Devices)

Es ist wichtig, einen PFD zu verwenden, der bei hohen Frequenzen arbeiten kann, da dies den Bedarf an Teilern minimiert, die das In-Band-Rauschverhalten beeinträchtigen können. Die Phasenvergleichsfrequenz von 1,3 GHz des HMC3716 von Analog Devices macht ihn ideal für den Einsatz im ZF-Bereich des ADF4401A. Die Fähigkeit einer solchen Schaltung, sowohl die Frequenz als auch die Phase zu vergleichen, macht zusätzliche Schaltungen zur Steuerung der Frequenz auf die beabsichtigte Ausgangsfrequenz überflüssig. Der HMC3716 wird zum externen PFD, um die Offsetschleife zu vervollständigen. Der hochfrequente Arbeitsbereich und das extrem niedrige Phasenrauschen des HMC3716 ermöglichen die Entwicklung von Schleifenfiltern mit großer Bandbreite.

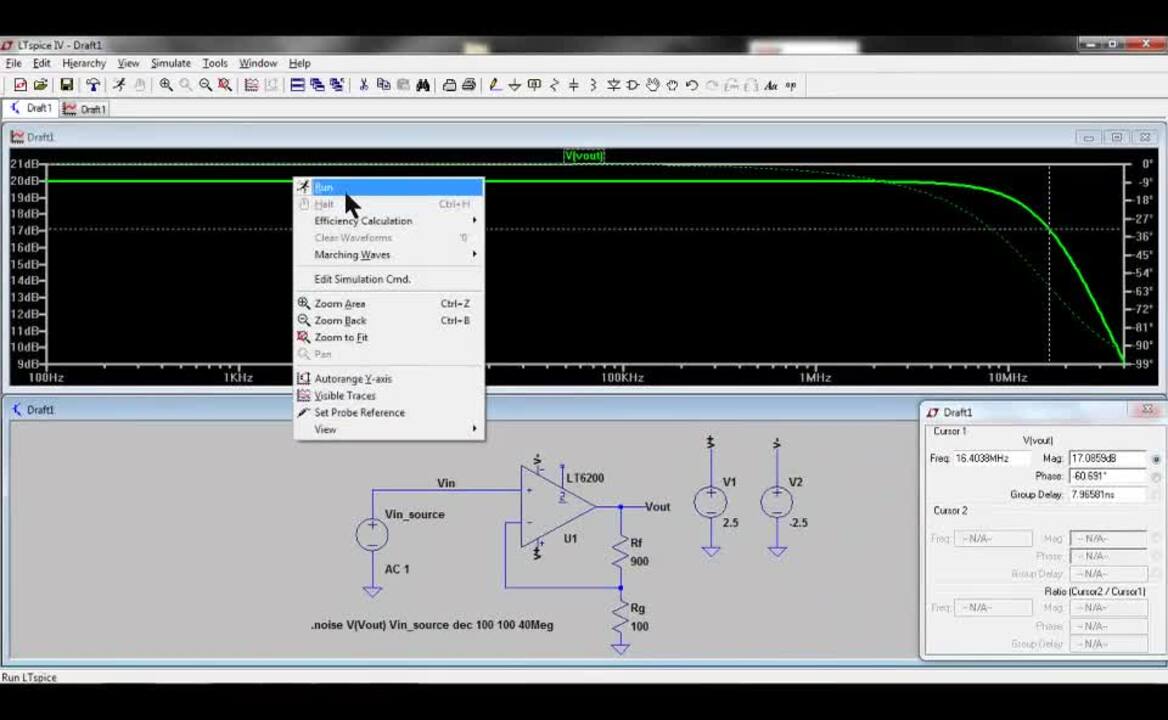

In Abbildung 7 dämpft der Operationsverstärker LT6200 mit einer LPF-Konfiguration hochfrequente Störimpulse, während der Schalter ADG1219 die Translationsschleife des Systems vervollständigt.

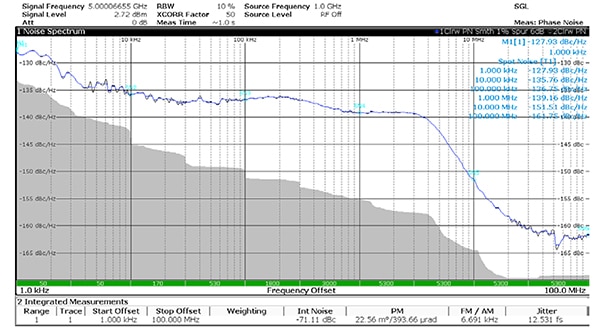

Die Evaluierungskonfiguration EV-ADF4401ASD2Z erstellt In-Band-Rauschdiagramme und Jitter-Messungen, wie in Abbildung 8 dargestellt.

Abbildung 8: Phasenrauschen eines einzelnen Seitenbands bei 5 GHz Ausgang, mit einer externen HMC3716-Referenz von 500 MHz und externem LO bei 4,5 GHz. (Bildquelle: Analog Devices)

Abbildung 8: Phasenrauschen eines einzelnen Seitenbands bei 5 GHz Ausgang, mit einer externen HMC3716-Referenz von 500 MHz und externem LO bei 4,5 GHz. (Bildquelle: Analog Devices)

In Abbildung 8 ist der LO2- und HMC3716-Eingang ein HF- und Mikrowellensignalgenerator SMA100B. Das LO2-In-Band-Rauschen des Evaluierungsboards beträgt etwa -135 dBc/Hz, was bei niedrigen Offsets bis zu 300 kHz auffällt. LO2, ADF4401A-Modul, HMC3716-PFD und Schleifenfilter tragen zu einem In-Band-Rauschen von etwa -140 dBc/Hz bei. Das interne Phasenrauschen tritt zwischen 5 MHz und 50 MHz auf, und das Phasenrauschen des Geräts liegt bei etwa -160 dBc/Hz. Zusammen ergibt sich ein Effektivwert des Jitters von insgesamt 12,53 fs.

Fazit

Highspeed-Instrumentierungssysteme erfordern extrem jitterarme Taktgeber, um sicherzustellen, dass die Ausgabedaten unverfälscht bleiben. Die Herausforderung für Ingenieure besteht darin, geeignete Komponenten zu finden, die das Highspeed-Gigahertz-Taktsystem bilden können. Die Translationsschleife ADF4401A vereinfacht die Bausteinauswahl für den Aufbau des Taktsystems erheblich und bietet ein kompaktes Modul, das einen geringen Jitter bei höheren Frequenzen gewährleistet und gleichzeitig den Platzbedarf auf der Leiterplatte, die Kosten und die Markteinführungszeit reduziert.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.