Gehäuse-Innovation macht Energieeffizienz bei Wearables möglich

Zur Verfügung gestellt von Europäische Fachredakteure von DigiKey

2014-12-09

Bei Wearables ist die Größe ein wichtiger Faktor bezüglich der Auswahl von Komponenten, auch der für die Stromversorgung. Es kommen DC/DC-Wandler mit einer hohen Wandlereffizienz auf den Markt, die außerdem die Platinenfläche durch Integration des Wandlungs-Controllers und Auslagerung von passiven Bausteinen in ein System-in-package-Modul reduzieren und so zur Verringerung der Große und zur Vereinfachung des Layouts beitragen. In diesem Artikel wird untersucht, inwiefern die Gehäuseintegration zur Reduzierung der Größe von Schaltwandlern für Wearables beiträgt und welche Design-Überlegungen bei der Arbeit mit diesen Bausteinen auftreten.

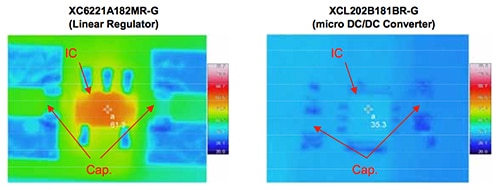

Beim Design von Wearables treten mehrere Herausforderungen auf, aber eines der wesentlichen Elemente ist die Energieeffizienz, nicht nur bezüglich Energie, sondern auch bezüglich der Größe. Diese Geräte werden über lange Zeit getragen. Sie benötigen daher eine hohe Akku-Autonomie. Wegen ihrer Nähe zur Haut sind hocheffiziente Wandler erforderlich. Dies kann eher von Schaltnetzteilen als von herkömmlichen, Low-Dropout-Reglern geleistet werden. Letztere wurden in der Vergangenheit wegen ihrer Kompaktheit bevorzugt. Der Entwurf von Schaltnetzteilen ist allerdings komplexer.

Obwohl die CMOS-Integration das Herunterskalieren von aktiven Komponenten ermöglicht hat, so auch von On-chip-Leistungstransistoren, beruhen herkömmliche Designs von DC/DC-Wandlern auf dem Einsatz von externen passiven Komponenten. Zwar benötigen diese einzelnen Bausteine selbst nicht viel Platz, aber zusammen erfordern Sie zum Betrieb des Wandlers viel Platz auf der Platine im Vergleich zum ursprünglichen SoC.

Beim Design von größeren Portables konnte die für die Stromversorgung benötigte Platinenfläche verschmerzt werden. Allerdings benötigen Wearables aufgrund Ihrer geringen Größe und den Platzanforderungen für den Akku zum Erreichen von langen Zeitabständen zwischen Aufladungen sehr viel Raum auf Kosten anderer Systemkomponenten.

DC/DC-Wandler für Wearables müssen nicht nur über eine hohe Wandlungseffizienz verfügen, sondern auch zur Minimierung der Platinenfläche beitragen, entweder durch Reduzierung der Anzahl der Bausteine oder durch Packen von mehr Bausteinen auf einer kleineren Fläche. Die geringe Größe hat erhebliche Auswirkungen auf das Platinen-Layout, da das Verschieben von Komponenten zur Minimierung von Rauschen und parasitärer Induktivität und Isolierung anderer empfindlicher Teile des Systems schwieriger wird. Daher sind rauscharme Komponenten und Topologien erforderlich, um zu gewährleisten, dass die Interferenz durch hocheffiziente Schaltwandler keine Auswirkungen auf andere Teile des Bausteins hat.

Durch Fortschritte bei der Materialverarbeitung bei passiven Bauteilen wie Kondensatoren und Induktoren konnte die Gesamtgröße verringert werden. Hersteller wie Murata, Texas Instruments und Torex haben die Vorzüge der Raumeinsparung maximiert und sind zur System-in-Package-Technologie (SiP) übergegangen, um noch mehr Platz auf der Platine einzusparen. Bei diesen Lösungen werden Steuerungs-IC und Induktor und in manchen Fällen auch Kondensatoren integriert.

Die SiP-Technologie ermöglicht die Integration von Komponenten in einem IC-kompatiblen Gehäuse. Erheblich kürzere Verbindungen und die Verwendung von fein abgestimmten Verteilungs-Layern innerhalb des Gehäuses verringern nicht nur die Induktivität und die Kapazität, sondern erlauben auch die Verwendung von erheblich kleineren Anschlusspads als bei Platinen.

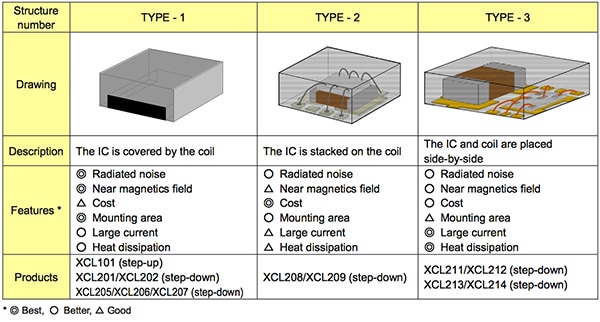

Auch wenn die SiP-Technologie den vom Wandler verbrauchten Platz minimiert, müssen Designentscheidungen getroffen werden, da eine einzelne SiP-Topologie nicht alle möglichen Anforderungen erfüllen kann. Ein großes Problem ist die Anordnung des Induktors innerhalb des Gehäuses. Daher hat Torex für seine XCL-Familie von Mikrowandlern drei SiP-Formen entwickelt. Jeder Mikroregler umfasst einen Schaltregler mit einem einzigen Ausgang und integriert Steuerungs-IC und Induktor. Die Gehäusestruktur wird durch Produktspezifikationen, IC, Induktor, thermisches Verhalten und weitere Charakteristika bestimmt. Für das Layout gibt es im Wesentlichen drei Varianten. Eine besteht darin, den Steuerungs-IC durch den Induktor zu überdecken. Dies ist die beste Lösung, was abgestrahltes Rauschen und Emissionen von magnetischen Feldern betrifft, führt aber meist zu höheren Kosten. Das Stapeln im Gehäuse reduziert den Platzverbrauch auf der Platine.

Die Anordnung des Steuerungs-ICs über dem Induktor reduziert die Kosten, da die zum Anschluss der Pads auf dem IC eingesetzte Drahtbonding-Technologie bei Stapeltechnologien sehr kostengünstig ist. Wenn der Steuerungs-IC vom Induktor überdeckt wird, können dieselben Bonding-Technologien eingesetzt werden. Allerdings erhöht sich bei dieser Bauform die magnetische Feldstärke in der Nähe der Platine. Sie kann daher nicht eingesetzt werden, wenn dies zu einem Problem werden könnte. Das abgestrahlte Rauschen ist auch etwas höher als bei der umgekehrten Konfiguration. Darüber hinaus verschlechtert sich das thermische Verhalten, da es keine Möglichkeit gibt, an der Unterseite des Steuerungs-ICs ein Wärmepad anzubringen, um die Wärme über die Platine abzuleiten. Auch fließt Wärme zwischen den übereinandergestapelten Komponenten.

Wenn IC und Induktor nebeneinander angeordnet werden, erhöht sich der Platzverbrauch, aber durch die erhöhte Platzeffizienz von Bonding-Pads bei SiPs wird der Platzbedarf relativ zu Implementierungen, bei denen die passiven Bausteine auf der Platine aufgereiht sind, dramatisch reduziert. Die Anordnung führt zu einer optimalen Wärmeableitung, vergleichsweise geringen Kosten, weniger Rauschen und kompatiblen magnetischen Feldern. Allerdings ist das Rauschverhalten der gestapelten Konfiguration mit unten liegendem IC besser.

Mikrowandler weisen oft ein besseres Rauschverhalten im Vergleich zu diskreten Implementierungen auf, da die Verbindungen kürzer sind. Das vorgefertigte Design reduziert darüber hinaus die Anzahl der vom Platinenentwickler zu treffenden Layout-Entscheidungen und beschleunigt damit die Entwicklung des Projekts. Die wichtigste Überlegungen sind Anordnung und Verlegung der Erd- und Versorgungsanschlüsse zur Minimierung der parasitären Induktivität.

Die Bausteine XCL201, 202, 205 und 206 sind synchrone DC/DC-Abwärtswandler mit integrierten Induktoren, die dem „Induktor oben“-Format entsprechen. Das gesamte SiP einschließlich Induktor nimmt eine Fläche von bis zu 2,5 mm x 2,0 mm auf der Platine ein. Die Gesamthöhe von Spule und DC/DC-Wandler wird durch ein neues ultra-flaches Gehäuse mit einer Höhe von 0,4 mm für DC/DC-Wandler-IC auf 1 mm begrenzt. Bei den einander ähnlichen XCL208 und 209 wird ein einfacherer Gehäuseaufbau eingesetzt: um Produktionskosten einzusparen, ist der Induktor unterhalb des Wandlers angebracht. Beim XCL208 und 209 kann die Ausgangsspannung eingestellt werden, aber die Energieeffizienz ist bei den Modellen XCL201 und 202 über den größten Teil der Lastbereichs höher. Zur Verringerung der Größe des Wandlerkern-Gehäuses werden zwei externe Kondensatoren benötigt.

Wie Torex hat auch Murata mit der LXDC-Familie eine Palette von DC/DC-Mikrowandlern entwickelt. Hier kann zwischen internen und externen Kondensatoren gewählt werden. Der LXDC2HL benötigt zur Reduzierung der Größe des Kern-SiPs zwei externe Kondensatoren aber das Gehäuse ist nur 2,5 mm x 2,0 mm groß. Das Induktorelement wird dabei durch ein im Gehäuse eingebettetes Ferrit-Substrat gebildet. Die Verbindungslänge zwischen dem Controller-IC und dem Induktor ist fast Null, was eine weitere Reduzierung der Rauschemission bewirkt. Das Ferrit-Mehrschichtsubstrat entsteht in einem Verfahren, bei dem bis zu 50 Schichten unterschiedlicher Ferrit-Materialien zusammengepresst werden. Dabei entsteht eine dreidimensionale Schaltung innerhalb des Substrats der Komponente.

Die Abwärtswandler-Bausteine sind für Stromquellen mit 2,3 V bis 5,5 V bestimmt, z. B. Lithium-Ionen-Akkus. Bei den Serien 2UR und 3EP sind Eingangs- und Ausgangskondensator oberhalb des Ferrit-Substrats integriert. Dadurch vergrößert sich das Gehäuse etwas, aber bei der Integration auf der Platine wird mehr Platz eingespart. Das Gehäuse des 3EP ist zwar mit 3.5 x 3.2 mm insgesamt etwas größer, aber der Wirkungsgrad ist höher – bis zu 92 % – und die maximale Last ist mit 1 A gegenüber den 600 mA des 2UR höher. Obwohl sich im Gehäuse des 2UR zwei Kondensatoren befinden, ist seine Platinenfläche mit 2,5 x 2,3 mm nur unwesentlich größer als die des 2HL. Die Bauweise der Murata-Mikrowandlers ist offen, um ein besseres thermisches Verhalten zu erreichen.

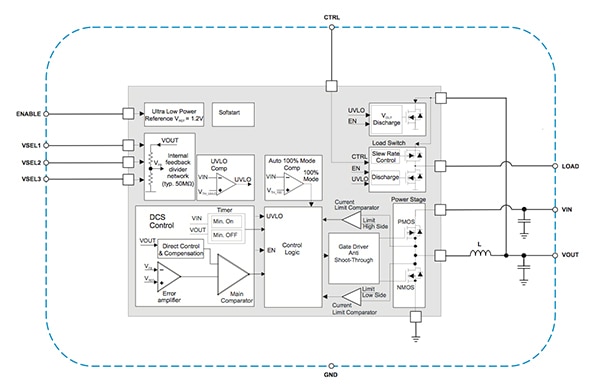

Beim TPS82740 von Texas Instruments wurde ein Abwärtswandler für Wearables einschließlich der erforderlichen passiven Komponenten in ein SiP mit 2,9 mm x 2,3 mm gepackt, wobei sich die erforderlichen passiven Komponenten als Array auf der oberen Fläche des Open-Framen-Gehäuses befinden. Abwärts-Mikrowandler können bei hoher Last vom PWM-Modus (Impulsbreitenmodulation) in einen energiesparenden Impulsmudus (PFM) umschalten. Beim TPS82740 wird ein neues Regelungsschema eingesetzt, durch das der Ruhestrom auf nur 360 nA reduziert wird. Der Baustein unterstützt bei Impulsbreitenmodulation Ausgangsstromstärken bis zu 200 mA. Wenn die Last unter 10 µA sinkt, schaltet er in einen energiesparenden Impulsmodus um.

Die DCS-Steuerung des TPS82740 verbindet Regelung im Hysterese- und Spannungs-Modus. Der Controller ist um eine Wechselstromschleife herum gebaut, die die Ausgangsspannung misst. Ein Komparator legt über diese Spannung die Schaltfrequenz fest. Diese ist bei stationären Betriebsbedingungen konstant und reagiert bei dynamischen Änderungen der Last sofort. Zur genauen Regelung der DC-Last wird Spannungs-Rückkopplungsschleife verwendet. Wenn die Laststromstärke sinkt, wird der Wandler zur Erhöhung des Wirkungsgrads in den Stromsparmodus versetzt. Die Schaltfrequenz ändert sich dabei fast linear mit der Laststromstärke. Im Impulsmodus generiert der Baustein einen einzelnen Schaltimpuls, um die Induktorstromstärke ansteigen zu lassen, und dann ein Ruheintervall, während dessen die meisten internen Schaltungen heruntergefahren werden, um Energie zu sparen. Während dieses Zeitraums wird der Laststrom vom Ausgangskondensator aufgefangen.

Durch Nutzung der Fortschritte der SiP-Technologie und von Regelungsalgorithmen versuchen die Hersteller, eine neue Generation von Wearables zu ermöglichen, für die durch mehr Platz für den lebenswichtigen Akku und einen höheren Gesamtwirkungsgrad eine größere Autonomie erreicht wird.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.