Wie man Firmware-Updates durchführt, ohne die Ausführung der Firmware zu stoppen

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2020-04-16

Die sensorbasierten Anwendungen des Internet der Dinge (Internet of Things, IoT) nehmen zu, und damit auch die Größe und Komplexität der Mikrocontroller-Firmware im IoT-Endpunkt. Diese Firmware muss effizienter werden, um die Ausführung zu beschleunigen, was ein Grund dafür ist, dass Flash-Firmware-Updates vor Ort notwendig sind. Für eine sichere Aktualisierung der Firmware im Feld ist es jedoch in der Regel erforderlich, die Ausführung der Firmware anzuhalten, während die Aktualisierung läuft. Abhängig von der Architektur, dem Umfang der Aktualisierung und der Netzwerkgeschwindigkeit kann dies in einer Minute oder in einer Stunde erfolgen. Bei kritischen Anwendungen kann diese Verzögerung inakzeptabel sein.

Dieser Artikel erläutert die Überlegungen zur Aktualisierung interruptgesteuerter Firmware im Feld und die Notwendigkeit, die Anwendungs-Firmware während der Aktualisierung weiter auszuführen. Anschließend wird der Mikrocontroller PIC32MZ2048EFH144T-I/PH von Microchip Technology vorgestellt und gezeigt, wie er zur Ausführung von Firmware verwendet werden kann, während gleichzeitig aktualisierte Firmware über ein Netzwerk empfangen wird.

Die Bedeutung von Firmware-Updates

Firmware wird aus vier Hauptgründen aktualisiert: um Fehler im Code zu korrigieren, um Funktionen hinzuzufügen oder zu verbessern, um Anpassungen an die Systemsicherheit vorzunehmen und um die Firmware effizienter zu machen. Die Code-Effizienz wird durch die Anzahl der Taktzyklen gemessen, die zur Ausführung einer bestimmten Aufgabe oder eines Threads benötigt werden. Je weniger Taktzyklen zur Ausführung einer Aufgabe erforderlich sind, desto effizienter ist der Code, was die Ausführung beschleunigt und normalerweise (nicht immer) die Codegröße reduziert. Dies gilt insbesondere für IoT-Sensor-basierte Endpunkte, da diese Anwendungen interruptgesteuert sind und daher schnell den Kontext wechseln müssen, wenn ein Sensor oder ein Peripheriegerät einen Interrupt erzeugt.

Zwei Faktoren, die die Effizienz von interrupt-gesteuerten IoT-Anwendungen beeinflussen, sind die Effizienz der Architektur und die Effizienz des Codes. Während es unpraktisch ist, die Architektur eines Mikrocontrollers im Feld zu ändern, ist es praktisch und normal, die Firmware des Mikrocontrollers zu aktualisieren, um die Effizienz zu verbessern.

Sensorbasierte Firmware ist fast immer interruptgesteuert. Intelligente Sensoren, die an eine serielle Schnittstelle eines Mikrocontrollers angeschlossen sind, können einen Interrupt für den Mikrocontroller erzeugen, um die normale Ausführung anzuhalten, so dass die Firmware zu einer Interrupt-Serviceroutine für diesen bestimmten Sensor vektoriell übertragen werden kann. Dies ist effizienter als Sensoren, die periodisch abgefragt werden müssen, um festzustellen, ob der Sensormesswert neue Daten zu übermitteln hat. Der Vorteil einer interruptgesteuerten Sensorstrategie besteht darin, dass der Mikrocontroller nur dann Taktzyklen für das Auslesen des Sensors aufwendet, wenn es nützliche Daten zu empfangen gibt. Beim Polling werden Taktzyklen verschwendet, wenn die Firmware auf den Sensor zugreifen muss, um Daten zu lesen, die verworfen werden, weil der Sensorwert nicht aktualisiert wurde.

Bei mehreren Sensoren und Aufgaben gibt es mehrere Unterprogramme und Unterbrechungsroutinen zu deren Verwaltung, wodurch die Codegröße zunimmt. Komplexer Code erfordert eine Form von Echtzeitbetriebssystem (RTOS), um all diese separaten Aufgaben zu verwalten. Das RTOS kann eine einfache, vom Software-Ingenieur geschriebene Firmware-Anwendung oder ein Standardprodukt sein. Das RTOS verwaltet die verschiedenen Firmware-Aufgaben, um sicherzustellen, dass jede einzelne Aufgabe innerhalb der für den ordnungsgemäßen Betrieb der Anwendung erforderlichen Zeit beginnt und endet. Wenn viele Aufgaben vom RTOS verwaltet werden müssen, ist es für die Anwendung vorteilhaft, wenn die Aufgaben in möglichst wenigen Taktzyklen erledigt werden. Dadurch wird verhindert, dass sich verschiedene Aufgaben gegenseitig verzögern.

Wenn eine Unterbrechung eintrifft, ist die Zeit, die benötigt wird, um die Unterbrechungs-Serviceroutine abzuschließen, meist eine Kombination aus drei Faktoren:

- Die Taktzyklen, die erforderlich sind, um die Unterbrechung zu erkennen und den Übergang zur Unterbrechungs-Service-Routine zu beginnen. Wenn die Aufgabe eine niedrigere Priorität hat als die laufende Aufgabe, wird dies verzögert, bis die aktuelle Aufgabe abgeschlossen ist. Dies ist anwendungsabhängig.

- Die Taktzyklen, die erforderlich sind, um den Kontext des aktuellen CPU-Zustands und den Vektor zur Interrupt-Serviceroutine zu speichern. Dies ist architekturabhängig und liegt außerhalb der Kontrolle des Software-Ingenieurs.

- Die zur Ausführung der Interrupt-Service-Routine erforderlichen Taktzyklen. Dies hängt sowohl von der Komplexität als auch von der Effizienz des vom Software-Ingenieur geschriebenen Codes ab.

Je effizienter die Firmware ist, desto unwahrscheinlicher ist ein Konflikt zwischen Aufgaben, die innerhalb eines bestimmten Zeitraums abgeschlossen werden müssen.

Flash-Firmware-Update-Speicheranforderungen

Systeme, die im Feld zuverlässig aktualisiert werden müssen, benötigen den doppelten geschätzten Flash-Programmspeicher, der für die Anwendung benötigt wird. Dies liegt daran, dass der Flash-Speicher groß genug sein muss, um sowohl die vorhandene Flash-Firmware als auch die aktualisierte Firmware zu enthalten. Bei kleinen Systemen, die nur vom internen Flash-Programmspeicher laufen, ist es jedoch üblich, die Code-Ausführung anzuhalten, während das Firmware-Update über das Netzwerk empfangen wird. Dies kann bei unternehmenskritischen Anwendungen inakzeptabel sein und widerspricht dem Ziel einer effizienten Firmware - d.h. Code, der gestoppt wird, läuft mit null Prozent Effizienz!

Ausführen von Firmware während der Flash-Aktualisierung

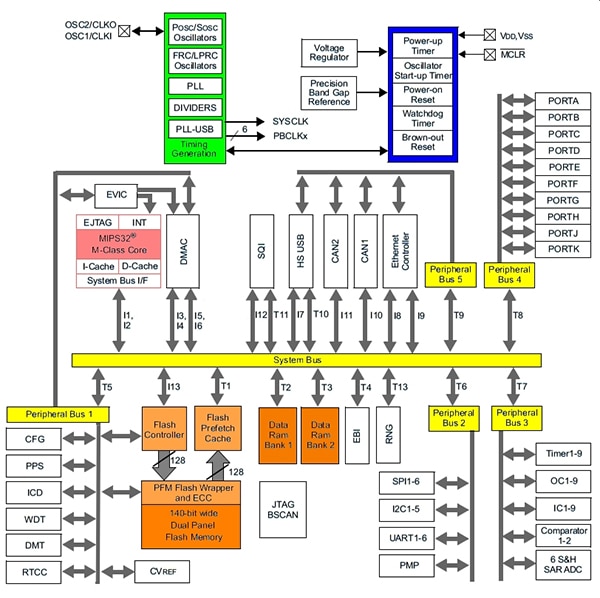

Ein hochleistungsfähiger Mikrocontroller, der Firmware ausführen kann, während der On-Chip-Flash-Speicher aktualisiert wird, ist der Mikrocontroller PIC32MZ2048EFH144T-I/PH von Microchip Technology (Abbildung 1). Der PIC32MZ2048EFH144T-I/PH basiert auf der M-Class MIPS32-Kernarchitektur mit einer Gleitkommaeinheit (FPU), die auf komplexe interruptgesteuerte IoT-Endpunkte abzielt. Er verfügt über 2 Megabyte (Mbytes) Programmspeicher-Flash und 512 Kilobyte (Kbytes) SRAM. Außerdem verfügt es über 160 KByte Boot-Flash. Der PIC32MZ2048EFH144T-I/PH-Kern kann bis zu 252 Megahertz (MHz) über einen Temperaturbereich von -40°C bis +85°C und bei 180 MHz über -40°C bis +125°C betrieben werden. Die Betriebsspannung liegt bei niedrigen 2,1 bis 3,6 Volt.

Es verfügt über neun 32-Bit-Erfassungs-/Vergleichstimer zur Unterstützung komplexer Firmware sowie zur Messung externer Signale.

Abbildung 1: Die 252-MHz-Mikrochip-Technologie PIC32MZ2048EFH144T-I/PH basiert auf der MIPS32 M-Klasse-Architektur und verfügt über eine Vielzahl von seriellen Schnittstellen zur Anbindung externer Sensoren. (Bildquelle: Microchip Technology)

Abbildung 1: Die 252-MHz-Mikrochip-Technologie PIC32MZ2048EFH144T-I/PH basiert auf der MIPS32 M-Klasse-Architektur und verfügt über eine Vielzahl von seriellen Schnittstellen zur Anbindung externer Sensoren. (Bildquelle: Microchip Technology)

Zu den externen seriellen Ports gehören neun UARTs und fünf I2C-Ports. Es gibt sechs SPI-Ports, die auch die Audio-I2S-Schnittstelle unterstützen. Ein 12-Bit-Analog-Digital-Wandler (ADC) mit 48 Eingängen kann Spannungen von analogen Präzisionssensoren messen. Mit diesen vielen seriellen Anschlüssen und ADC-Eingängen kann der PIC32MZ2048EFH144T-I/PH mit vielen externen Sensoren verbunden werden, was ihn für komplexe sensorbasierte IoT-Endpunkte geeignet macht. Zwei CAN 2.0b-Ports ermöglichen dem Mikrocontroller die Vernetzung mit industriellen und automobilen Netzwerken, die das gemeinsame CAN-Protokoll verwenden.

Ein Ethernet-Anschluss unterstützt 10/100Base-T-Netzwerke. Ein USB 2.0 Hi-Speed-Controller unterstützt eine externe Schnittstelle für zusätzliche Peripheriegeräte oder Debugging und unterstützt auch USB On-The-Go (OTG).

Jedes dieser Peripheriegeräte kann einen oder mehrere Interrupts erzeugen. Bei so vielen Sensoren und Unterbrechungsquellen wird die Aufrechterhaltung der Code-Effizienz zu einer Notwendigkeit.

Zur Verbesserung der Effizienz verfügt der MIPS32-CPU-Kern der M-Klasse über 32 32-Bit-Allzweckregister (GPRs). Dies verbessert die Effizienz, indem die Zugriffe auf den externen Speicher reduziert werden. Neben den üblichen Bitmengen- und klaren Befehlen unterstützt die M-Klasse auch Bit-Invertierungsbefehle mit einem Zyklus. Dies verbessert die RTOS-Effizienz, indem es die Effizienz der Handhabung von Semaphoren erhöht. Der Kern verfügt auch über eine fünfstufige Befehlspipeline, die die Effizienz durch Minimierung von Speicherzugriffskonflikten verbessert, was zu mehr Einzelzyklus-Befehlen führt.

Die M-Klasse MIPS32 verfügt außerdem über sieben GPR-Schattenregistersätze. Dies verbessert die Interrupt-Performance und den Kontextwechsel erheblich, da die vielen Taktzyklen, die zum Speichern der GPRs auf dem Stack erforderlich sind, entfallen. Mit sieben Schattenregistersätzen kann der Kern Unterbrechungen und Kontextwechsel sieben tief verschachteln, bevor er Taktzyklen damit verbringen muss, die GPRs auf dem Stack zu speichern.

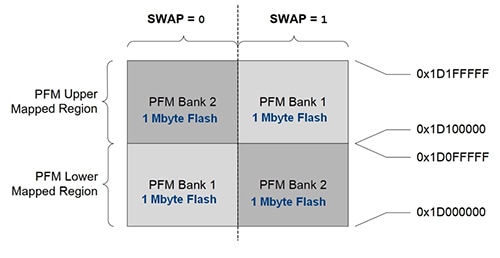

Der PIC32MZ2048EFH144T-I/PH verfügt über zwei 1-Mbyte-Bänke Programm-Flash-Speicher (PFM), die als PFM-Bank 1 und PFM-Bank 2 bezeichnet werden. Jeder PFM hat seinen eigenen dedizierten Boot-Flash-Speicher (BFM), der als BFM Bank 1 und BFM Bank 2 bezeichnet wird. Das BFM muss bei einer Aktualisierung des PFM nicht aktualisiert werden. Diese beiden getrennten Speicherbänke haben mehrere Vorteile. Beispielsweise unterstützt der Mikrocontroller Dual-Boot, so dass er beim Einschalten so konfiguriert werden kann, dass er von jeder Flash-Speicherbank bootet. Dadurch kann der Mikrocontroller zwei verschiedene Gerätekonfigurationen unterstützen.

Die beiden Flash-Bänke bieten außerdem den zusätzlichen Vorteil, dass die Firmware von einer Flash-Bank ausgeführt werden kann, während die Firmware in der anderen Flash-Bank aktualisiert wird. Microchip bezeichnet dies als Live-Update, auch als Runtime-Selbstprogrammierung (RTSP) bezeichnet. Wenn ein RTSP in einem aktiven IoT-Endpunkt initiiert wird, der Firmware aus der PFM-Bank 1 ausführt, wird die Firmware in Blöcken über das Netzwerk empfangen. Die empfohlene Methode zur Verwaltung von Firmware-Aktualisierungen über ein Netzwerk besteht darin, den Block der neuen Firmware im SRAM zu speichern. Nachdem ein kompletter Block empfangen wurde, kann die Firmware, die aus der PFM-Bank 1 ausgeführt wird, eine Programmiersequenz der SRAM-Daten in die PFM-Bank 2 initiieren. Während diese Firmware programmiert wird, kann die Ausführung der Firmware aus der PFM-Bank 1 fortgesetzt werden.

Wenn die Blockprogrammierung abgeschlossen ist, kann die Firmware den nächsten Codeblock über das Netzwerk anfordern und die Sequenz wiederholt sich. Dies wird so lange fortgesetzt, bis der Codeblock in der PFM-Bank 2 abgeschlossen ist. Sobald die Programmierung abgeschlossen ist, kann die Firmware den PIC32MZ2048EFH144T-I/PH beim nächsten Reset konfigurieren, um von der BFM-Bank 2 zu booten und die neue Firmware in der PFM-Bank 2 auszuführen, indem das SWAP-Bit im NVMCON-Konfigurationsregister gelöscht wird (Abbildung 2). Wenn die PIC32MZ2048EFH144T-I/PH-Firmware erneut aktualisiert werden muss, während SWAP=0, kann die Firmware aus der PFM-Bank 2 heraus ausgeführt werden, während gleichzeitig die PFM-Bank 1 aktualisiert wird.

Abbildung 2: Der Mikrocontroller PIC32MZ2048EFH144T-I/PH verfügt über zwei unabhängige PFM-Bänke. Wenn SWAP=1, kann die Firmware der PFM-Bank 1 ausgehen, während die PFM-Bank 2 aktualisiert wird. Durch Löschen von SWAP=0 kann der Mikrocontroller aus der PFM-Bank 2 booten. (Bildquelle: Microchip Technology)

Abbildung 2: Der Mikrocontroller PIC32MZ2048EFH144T-I/PH verfügt über zwei unabhängige PFM-Bänke. Wenn SWAP=1, kann die Firmware der PFM-Bank 1 ausgehen, während die PFM-Bank 2 aktualisiert wird. Durch Löschen von SWAP=0 kann der Mikrocontroller aus der PFM-Bank 2 booten. (Bildquelle: Microchip Technology)

Der Status des SWAP-Bits kann je nach den Anforderungen der Firmware entweder vom BFM oder vom PFM aus geändert werden.

Entwicklung von Dual-Boot-Firmware

Für die Entwicklung mit dem Mikrocontroller PIC32MZ2048EFH144T-I/PH bietet Microchip Technology das Starterkit DM320007 PIC32MZ an (Abbildung 3). Diese Karte unterstützt mehrere serielle Schnittstellen, die sowohl dedizierte Steckverbinder als auch Stiftleisten verwenden. Ein USB-Host-Anschluss wird für das Debugging verwendet, während ein USB-OTG-Anschluss für die Anwendung verwendet werden kann. Ein USB-zu-UART/I2C-Anschluss erzeugt, wenn er an einen PC-USB-Anschluss angeschlossen wird, einen virtuellen COM-Anschluss auf einem angeschlossenen Host-PC. Dadurch kann der Host-PC mit dem I2C-Port des PIC32MZ kommunizieren.

Abbildung 3: Das kompakte Starterkit DM320007 von Microchip Technology unterstützt die Entwicklung und das Testen von USB- und Ethernet-Anwendungen mit dem Mikrocontroller PIC32MZ2048EFH144T-I/PH. Es umfasst Anschlüsse für USB OTG, USB Host, 10/100 Ethernet und UART/I2C. (Bildquelle: Microchip Technology)

Abbildung 3: Das kompakte Starterkit DM320007 von Microchip Technology unterstützt die Entwicklung und das Testen von USB- und Ethernet-Anwendungen mit dem Mikrocontroller PIC32MZ2048EFH144T-I/PH. Es umfasst Anschlüsse für USB OTG, USB Host, 10/100 Ethernet und UART/I2C. (Bildquelle: Microchip Technology)

Ein 40-poliger Erweiterungssteckverbinder ermöglicht den Zugriff auf zusätzliche I2C-, SPI- und UART-Ports sowie auf GPIO-Pins (General Purpose I/O) des PIC32MZ EF. Es gibt drei Drucktasten und drei LEDs, die per Firmware konfiguriert werden können.

Fazit

IoT-Sensor-Endpunkte in kritischen Systemen stellen aufgrund der erhöhten Code-Komplexität höhere Speicheranforderungen. Je komplexer der Code ist, desto mehr ist es notwendig, die Effizienz der Firmware zu verbessern, um die Reaktionszeiten der Kontextumschaltung in der Firmware zu verbessern. Durch die Auswahl eines Mikrocontrollers, der Interrupt-gesteuerten Code effizient ausführen kann, der gleichzeitig Firmware abrufen und aktualisieren kann, können Entwickler die Zuverlässigkeit kritischer IoT-Anwendungen ohne Leistungseinbußen verbessern.

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.