Entwerfen Sie eine effektivere Blindleistungskompensation unter Verwendung von Halbleitern mit großer Bandlücke und digitaler Regelung

Zur Verfügung gestellt von Nordamerikanische Fachredakteure von DigiKey

2020-10-14

Die Blindleistungskompensation (PFC) ist notwendig, um die Effizienz von netzbetriebenen Wechselstromgeräten einschließlich AC/DC-Netzteilen, Batterieladegeräten, batteriegestützten Energiespeichersystemen, Motorantrieben und unterbrechungsfreien Stromversorgungen zu maximieren. Ihre Bedeutung ist so groß, dass es Vorschriften gibt, die Mindestwerte für den Leistungsfaktor (PF) für bestimmte Arten von elektronischen Geräten vorschreiben.

Um diesen Vorschriften angesichts des ständigen Drucks zur Verbesserung der Gesamtleistung bei immer kleiner werdenden Formfaktoren gerecht zu werden, wenden sich die Entwickler aktiven PFC-Designs zu, die die Vorteile digitaler Steuerungstechniken und Halbleiter mit großer Bandlücke wie Siliziumkarbid (SiC) und Galliumnitrid (GaN) nutzen.

Dieser Artikel gibt einen Überblick über PF-Konzepte und -Definitionen, einschließlich der unterschiedlichen Definitionen zwischen IEEE und IEC und der zugehörigen Normen. Anschließend werden Lösungen für die PFC von Anbietern wie STMicroelectronics, Transphorm, Microchip Technology und Infineon Technologies vorgestellt, mit denen Entwickler PFC unter Verwendung von Halbleitern mit großer Bandlücke und digitaler Steuerung implementieren können, einschließlich der Verwendung von Evaluierungsboards.

Was ist Blindleistungskompensation und warum ist sie notwendig?

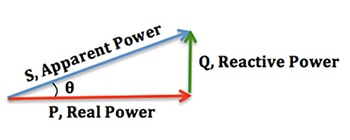

PF ist ein Maß für die Höhe der Blindleistung in einem System. Blindleistung ist keine Wirkleistung, sondern stellt die Auswirkung von Volt und Ampere dar, die zueinander phasenverschoben sind (Abbildung 1). Da sie phasenverschoben sind, können sie keinen wirksamen Beitrag zur Arbeit leisten, erscheinen aber dennoch als Last auf der Wechselstromversorgungsleitung. Die Höhe der Blindleistung in einem System ist ein Maß für den Grad der Ineffizienz der Energieübertragung. Aktive PFC verwendet Leistungselektronik, um die Phase und/oder Form der von einer Last gezogenen Stromwellenform zu ändern, um den PF zu verbessern. Die Verwendung von PFC erhöht die Effizienz des Gesamtsystems.

Abbildung 1: PF ist definiert als der Kosinus von θ und stellt das Verhältnis der von der Last aufgenommenen Wirkleistung zu der in der Schaltung fließenden Scheinleistung dar. Die Differenz zwischen den beiden wird durch die Blindleistung verursacht. Wenn die Blindleistung Null wird, erscheint die Last als rein ohmsche Last, Schein- und Wirkleistung gleichen sich aus, und der PF wird 1,0. (Bildquelle: Wikipedia)

Abbildung 1: PF ist definiert als der Kosinus von θ und stellt das Verhältnis der von der Last aufgenommenen Wirkleistung zu der in der Schaltung fließenden Scheinleistung dar. Die Differenz zwischen den beiden wird durch die Blindleistung verursacht. Wenn die Blindleistung Null wird, erscheint die Last als rein ohmsche Last, Schein- und Wirkleistung gleichen sich aus, und der PF wird 1,0. (Bildquelle: Wikipedia)

Ein schlechter PF kann bei linearen oder nichtlinearen Lasten auftreten. Nichtlineare Lasten verzerren die Spannungs- oder Stromwellenform oder beide. Wenn nichtlineare Lasten beteiligt sind, wird der PF auch als Leistungsverzerrungsfaktor bezeichnet.

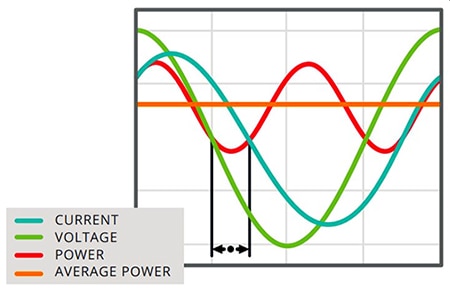

Eine lineare Last verzerrt nicht die Form der Eingangswellenform, kann jedoch aufgrund ihrer Induktivität und/oder Kapazität das relative Timing (Phase) zwischen Spannung und Strom ändern (Abbildung 2). Elektrische Schaltkreise mit vorwiegend ohmschen Lasten (z.B. Glühlampen und Heizelemente) haben einen PF von fast 1,0, aber Schaltkreise mit induktiven oder kapazitiven Lasten (z.B. Schaltnetzteile, Elektromotoren, Magnetventile, Transformatoren und Lampenvorschaltgeräte) können einen PF deutlich unter 1,0 haben.

Abbildung 2: Momentane und mittlere Leistung, berechnet aus Wechselspannung und -strom mit einem nacheilenden PF (d.h., der Strom eilt der Spannung hinterher) von 0,71 bei einer linearen Last. (Bildquelle: CUI, Inc.)

Abbildung 2: Momentane und mittlere Leistung, berechnet aus Wechselspannung und -strom mit einem nacheilenden PF (d.h., der Strom eilt der Spannung hinterher) von 0,71 bei einer linearen Last. (Bildquelle: CUI, Inc.)

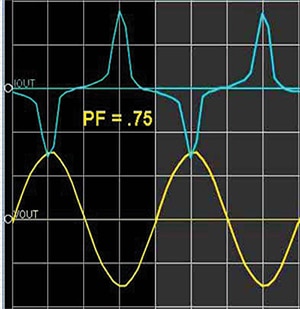

Die meisten elektronischen Lasten sind nicht linear. Beispiele für nichtlineare Lasten sind Schaltnetzteile und Bogenentladungsgeräte wie Leuchtstofflampen, Elektroschweißmaschinen oder Lichtbogenöfen. Da der Strom in diesen Systemen durch einen Schaltvorgang unterbrochen wird, enthält der Strom Frequenzkomponenten, die ein Vielfaches der Netzfrequenz sind. Der Leistungsverzerrungsfaktor ist ein Maß dafür, um wie viel die harmonische Verzerrung eines Laststroms die durchschnittliche an die Last übertragene Leistung verringert.

Abbildung 3: Sinusförmige Spannung (gelb) und nicht-sinusförmiger Strom (blau) ergeben einen Leistungsverzerrungsfaktor von 0,75 für dieses Computer-Netzteil, das eine nichtlineare Last darstellt. (Bildquelle: Wikipedia)

Abbildung 3: Sinusförmige Spannung (gelb) und nicht-sinusförmiger Strom (blau) ergeben einen Leistungsverzerrungsfaktor von 0,75 für dieses Computer-Netzteil, das eine nichtlineare Last darstellt. (Bildquelle: Wikipedia)

Der Unterschied zwischen nacheilendem und voreilendem PF

Ein nacheilender PF bedeutet, dass der Strom der Spannung nacheilt (hinter der Spannung liegt), und ein voreilender PF bedeutet, dass der Strom der Spannung vorauseilt (vor der Spannung liegt). Bei induktiven Lasten (z.B. Induktionsmotoren, Spulen und einigen Lampen) bleibt der Strom hinter der Spannung zurück, wodurch ein nacheilender PF entsteht. Bei kapazitiven Lasten (z. B. synchronen Kondensatoren, Kondensatorbänken und elektronischen Stromrichtern) eilt der Strom der Spannung voraus, was zu einem voreilenden PF führt.

Der Unterschied zwischen „nacheilend“ und „voreilend“ ist nicht gleichbedeutend mit einem positiven oder negativen Wert. Das negative und positive Vorzeichen, das einem PF-Wert vorausgeht, wird durch die verwendete Norm bestimmt - entweder die IEEE oder die IEC.

PF und IEEE versus IEC

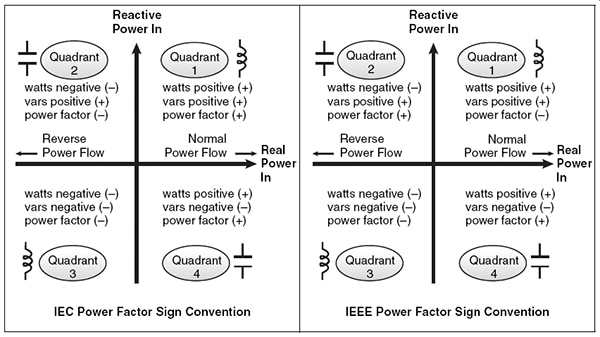

Die Diagramme in Abbildung 4 zeigen die Korrelation zwischen Kilowatt-Leistung (kW), Volt-Ampere-Blindleistung (var), Leistungsfaktor und induktiven oder kapazitiven Lasten sowohl für die IEEE- als auch für die IEC-Normen. Jede Organisation verwendet unterschiedliche Metriken zur Klassifizierung des PF.

Abbildung 4: Gemäß IEC (links) hängt das Vorzeichen des Leistungsfaktors ausschließlich von der Richtung des Wirkleistungsflusses ab und ist unabhängig davon, ob die Last induktiv oder kapazitiv ist. Gemäß IEEE (rechts) hängt das Vorzeichen des Leistungsfaktors ausschließlich von der Art der Last (d.h. kapazitiv oder induktiv) ab. In diesem Fall ist es unabhängig von der Richtung des Wirkleistungsflusses. (Bildquelle: Schneider Electric)

Abbildung 4: Gemäß IEC (links) hängt das Vorzeichen des Leistungsfaktors ausschließlich von der Richtung des Wirkleistungsflusses ab und ist unabhängig davon, ob die Last induktiv oder kapazitiv ist. Gemäß IEEE (rechts) hängt das Vorzeichen des Leistungsfaktors ausschließlich von der Art der Last (d.h. kapazitiv oder induktiv) ab. In diesem Fall ist es unabhängig von der Richtung des Wirkleistungsflusses. (Bildquelle: Schneider Electric)

Gemäß IEC (linke Seite von Abbildung 4) hängt das Vorzeichen für den PF ausschließlich von der Richtung des Wirkleistungsflusses ab und ist unabhängig davon, ob die Last induktiv oder kapazitiv ist. Gemäß IEEE (rechte Seite von Abbildung 4) hängt das PF-Vorzeichen ausschließlich von der Art der Last (d.h. kapazitiv oder induktiv) ab. In diesem Fall ist es unabhängig von der Richtung des Wirkleistungsflusses. Bei einer induktiven Last ist der PF negativ. Bei einer kapazitiven Last ist der PF positiv.

PF-Normen

Regulierungsbehörden wie die EU haben harmonische Grenzen festgelegt, um die PF zu verbessern. Um der aktuellen EU-Norm EN61000-3-2 (die auf IEC 61000-3-2 basiert) zu entsprechen, müssen alle Schaltnetzteile mit einer Ausgangsleistung von mehr als 75 Watt PFC enthalten. Die 80-PLUS-Netzteilzertifizierung durch EnergyStar erfordert einen PF von 0,9 oder mehr bei 100% der Nennausgangsleistung und erfordert aktive PFC. Die neueste Ausgabe der IEC-Norm zum Zeitpunkt der Abfassung dieses Artikels ist: IEC 61000-3-2:2018, „Elektromagnetische Verträglichkeit (EMV) - Teil 3-2: Grenzwerte - Grenzwerte für Oberschwingungsstromemissionen (Geräte-Eingangsstrom ≤16 A pro Phase)“.

Unkorrigierte Schaltnetzteile entsprechen nicht den aktuellen PFC-Normen. Eine Überlegung, die sich auf den PF auswirkt, ist, welche Art von Wechselstromeingang verwendet wird: einphasig oder dreiphasig. Einphasige unkorrigierte Schaltnetzteile haben typischerweise einen PF von etwa 0,65 bis 0,75 (unter Verwendung der oben beschriebenen IEEE-Konvention für das PF-Zeichen). Der Grund dafür ist, dass die meisten Einheiten ein Gleichrichter/Kondensator-Frontend zur Erzeugung einer Zwischenkreisspannung verwenden. Bei dieser Konfiguration wird nur an der Spitze jedes Leitungszyklus Strom gezogen, wodurch schmale, hohe Stromimpulse erzeugt werden, die zu einem schlechten PF führen (siehe Abbildung 3, oben).

Dreiphasige, unkorrigierte Schaltnetzteile haben einen höheren PF, der oft nahe 0,85 liegt (auch unter Verwendung der IEEE-Konvention für das PF-Zeichen). Denn obwohl ein Gleichrichter/Kondensator zur Erzeugung einer Gleichstrom-Busspannung verwendet wird, gibt es drei Phasen, die den Gesamt-PF additiv verbessern. Allerdings können weder ein- noch dreiphasige Schaltnetzteile die aktuellen PF-Vorschriften ohne die Verwendung einer aktiven PF-Korrekturschaltung erfüllen.

Verwendung von WBG-Halbleitern und digitaler Regelung zum Entwurf aktiver PFC

Der Einsatz von digitalen Regelungstechniken und Leistungshalbleitern mit großer Bandlücke, einschließlich GaN und SiC, bietet Entwicklern neue Optionen für aktive PFC-Schaltungen, die im Vergleich zu aktiven PFC-Designs, die auf analoger Regelung oder passiven PFC-Designs basieren, höhere Wirkungsgrade und höhere Leistungsdichten liefern können.

Entwickler können analoge Regler durch fortschrittliche digitale Regelungstechniken ersetzen oder die analoge Regelung durch zusätzliche digitale Steuerelemente, einschließlich Mikrocontroller, ergänzen, um die maximale PFC-Leistung zu erzielen. In einigen Fällen können auch WBG-Halbleiter zur Verbesserung der PFC-Leistung eingesetzt werden.

Sinkende Komponentenkosten beschleunigten die Implementierung von zwei verschiedenen Methoden für PFC: verschachtelte (interleaved) Designs und brückenlose Designs. Jeder Ansatz bringt eine andere Reihe von Vorteilen:

- Vorteile verschachtelter (interleaved) PFC:

- Höherer Wirkungsgrad

- Verbesserte Wärmeabführung

- Reduzierter Effektivstrom durch die PFC-Stufe

- Modularität

- Vorteile brückenloser PFC:

- Höherer Wirkungsgrad

- Halbiert die Verluste bei der Eingangsgleichrichtung

- Verbesserte Wärmeabführung

- Höhere Leistungsdichte

Dreikanaliger verschachtelter (interleaved) PFC-Controller kombiniert analoge und digitale Regelung

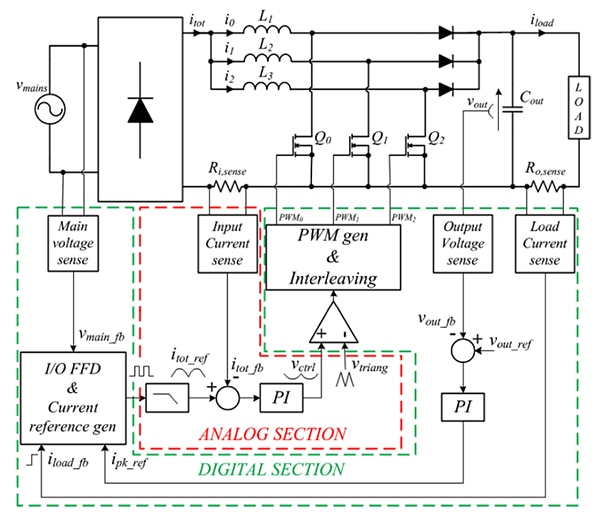

Der Controller STNRGPF01 von STMicroelectronics ist ein konfigurierbarer ASIC, der digitale und analoge Regelung kombiniert und bis zu drei Kanäle in einer verschachtelten PFC ansteuern kann (Abbildung 5). Die Komponente arbeitet im kontinuierlichen Leitungsmodus (CCM) bei fester Frequenz mit Regelung des mittleren Stroms und implementiert eine Mischsignalregelung (analog/digital). Die analoge innere Stromschleife wird durch Hardware ausgeführt, wodurch eine zyklusweise Regelung gewährleistet wird. Die äußere Spannungsschleife erfolgt mithilfe eines digitalen PI-Reglers (Proportional-Integral-Regler) mit einem schnellen dynamischen Ansprechverhalten.

Abbildung 5: Ein funktionales Blockdiagramm des STNRGPF01 zeigt den inneren analogen Reglerteil (rot) und den äußeren digitalen Reglerteil (grün) in einer dreiphasigen verschachtelten PFC-Anwendung. (Bildquelle: STMicroelectronics)

Abbildung 5: Ein funktionales Blockdiagramm des STNRGPF01 zeigt den inneren analogen Reglerteil (rot) und den äußeren digitalen Reglerteil (grün) in einer dreiphasigen verschachtelten PFC-Anwendung. (Bildquelle: STMicroelectronics)

Der STNRGPF01 implementiert eine flexible Phasenabwurfstrategie, die die korrekte Anzahl von PFC-Kanälen auf der Grundlage des tatsächlichen Lastzustands ermöglicht. Mit dieser Funktion ist der STNRGPF01 stets in der Lage, die höchste Energieeffizienz über einen weiten Bereich von Laststromanforderungen zu gewährleisten.

Der Regler implementiert mehrere Funktionen: Einschaltstromregelung, Sanftstart, Burst-Mode-Kühlungsmanagement und Statusanzeige. Er verfügt zudem über einen vollständigen Satz eingebetteter Schutzvorrichtungen gegen Überspannung, Überstrom und thermische Fehler.

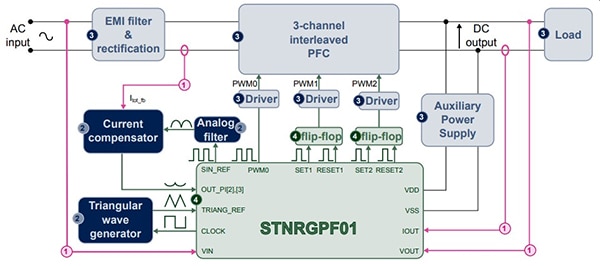

Um Entwicklern den Einstieg zu erleichtern, bietet STMicroelectronics auch das 3 kW Evaluierungsboard STEVAL-IPFC01V1 für das PFC-Energiemanagement an, das auf dem STNRGPF01 basiert (Abbildung 6). Merkmale und Spezifikationen umfassen:

- Eingangsspannungsbereich: 90 bis 265 VAC

- Netzfrequenzbereich: 47 bis 63 Hertz (Hz)

- Maximale Ausgangsleistung: 3 kW bei 230 Volt

- Ausgangsspannung: 400 Volt

- PF > 0,98 bei 20 % Last

- Gesamte harmonische Verzerrung: <5% bei 20% Last

- Mischsignalregelung

- Schaltfrequenz: 111 kHz

- Zyklusweise regelung (analoge Stromregelschleife)

- Eingangsspannungs- und Last-Vorwärtskopplung

- Phasenabwurf

- Betrieb im Burst-Modus

Abbildung 6: Blockdiagramm des STEVAL-IPFC01V1 zeigt: 1. I/O-Messsignale; 2. Analogschaltkreis; 3. Leistungsstufe; 4. Digitaler Regelabschnitt mit digitalem Regler STNRGPF01; in einer dreiphasigen verschachtelten PFC. (Bildquelle: STMicroelectronics)

Abbildung 6: Blockdiagramm des STEVAL-IPFC01V1 zeigt: 1. I/O-Messsignale; 2. Analogschaltkreis; 3. Leistungsstufe; 4. Digitaler Regelabschnitt mit digitalem Regler STNRGPF01; in einer dreiphasigen verschachtelten PFC. (Bildquelle: STMicroelectronics)

Zusätzlich zum Mischsignalregler STNRGPF01 enthält dieses Evaluierungsboard N-Kanal-Silizium-Leistungs-MOSFETs STW40N60M2 für 600 Volt, 34 Ampere (A) mit niedrigem Qg und Gate-Treiber-ICs PM8834TR.

Brückenlose Totempole-PFC mit GaN-FETs

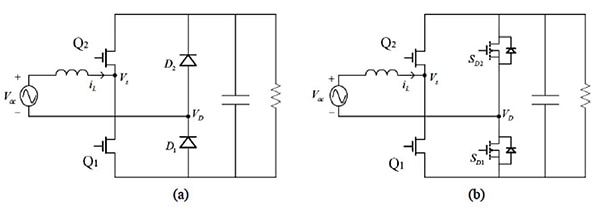

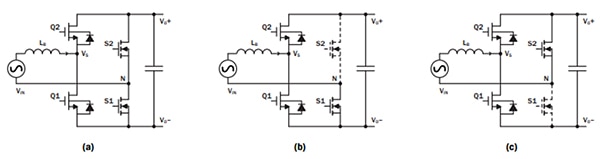

Brückenlose PFC-Topologien wurden entwickelt, um die Spannungsabfälle und Ineffizienzen zu eliminieren, die mit dem Einsatz der Dioden-Brückengleichrichtung verbunden sind. Die brückenlose Totempole-PFC wurden durch das Aufkommen von WBG-Leistungshalbleitern wie GaN und SiC ermöglicht (Abbildung 7). In einem konventionellen Totempole-Design (a) werden zwei GaN-FETs und zwei Dioden für die Netzgleichrichtung verwendet. Bei einer brückenlosen Totempole-Modifikation (b) werden die Dioden durch zwei niederohmige Silizium-MOSFETs ersetzt, um die Strom-Spannungsabfälle (IV) der Dioden zu ersetzen und die Effizienz zu verbessern.

Abbildung 7: In einem konventionellen Totempole-Design (a) werden zwei GaN-FETs und zwei Dioden für die Netzgleichrichtung verwendet; in einer modifizierten Schaltung (b) werden die Dioden durch zwei niederohmige Silizium-MOSFETs ersetzt, um die Strom-Spannungsabfälle der Dioden zu ersetzen und die Effizienz im brückenlosen Totempole zu verbessern. (Bildquelle: Transphorm)

Abbildung 7: In einem konventionellen Totempole-Design (a) werden zwei GaN-FETs und zwei Dioden für die Netzgleichrichtung verwendet; in einer modifizierten Schaltung (b) werden die Dioden durch zwei niederohmige Silizium-MOSFETs ersetzt, um die Strom-Spannungsabfälle der Dioden zu ersetzen und die Effizienz im brückenlosen Totempole zu verbessern. (Bildquelle: Transphorm)

Die im Vergleich zu Silizium-MOSFETs deutlich geringere Umkehrerholungsladung (Qrr) der GaN-Transistoren mit hoher Elektronenbeweglichkeit (HEMTs) macht brückenlose Totempole-Designs praktikabel (Abbildung 8). In diesem vereinfachten Schema einer Totempole-PFC in CCM liegt der Schwerpunkt auf der Minimierung von Leitungsverlusten.

Abbildung 8: Das vereinfachte Schema einer Totempole-PFC im CCM-Modus umfasst zwei schnell schaltende GaN-HEMTs (Q1 und Q2), die bei einer hohen Pulsbreitenmodulationsfrequenz arbeiten und als Aufwärtswandler fungieren, sowie zwei sehr niederohmige MOSFETs (S1 und S2), die bei einer viel langsameren Netzfrequenz (50Hz/60Hz) arbeiten. (Bildquelle: Transphorm)

Abbildung 8: Das vereinfachte Schema einer Totempole-PFC im CCM-Modus umfasst zwei schnell schaltende GaN-HEMTs (Q1 und Q2), die bei einer hohen Pulsbreitenmodulationsfrequenz arbeiten und als Aufwärtswandler fungieren, sowie zwei sehr niederohmige MOSFETs (S1 und S2), die bei einer viel langsameren Netzfrequenz (50Hz/60Hz) arbeiten. (Bildquelle: Transphorm)

Die Schaltung besteht aus zwei schnell schaltenden GaN-HEMTs (Q1 und Q2) und zwei sehr niederohmigen MOSFETs (S1 und S2). Q1 und Q2 arbeiten mit einer hohen Pulsbreitenmodulationsfrequenz (PWM) und fungieren als Aufwärtswandler. S1 und S2 arbeiten mit einer viel langsameren Netzfrequenz (50 Hz/60 Hz) und fungieren als synchronisierter Gleichrichter. Der Primärstrompfad umfasst nur einen schnellen und einen langsamen Schalter ohne Diodenabfall. Die Rolle von S1 und S2 ist die eines Synchrongleichrichters, wie in 8(b) und 8(c) dargestellt. Während des positiven AC-Zyklus ist S1 eingeschaltet und S2 ausgeschaltet, wodurch der an den Minuspol angeschlossene AC-Neutralleiter an den DC-Ausgang gezwungen wird. Für den negativen Zyklus gilt das Gegenteil.

Um den CCM-Betrieb zu ermöglichen, muss die Substratdiode des Slave-Transistors als Rücklaufdiode fungieren, damit der Induktionsstrom während der Totzeit fließen kann. Der Diodenstrom muss jedoch schnell auf Null sinken und in den umgekehrten Sperrzustand übergehen, sobald der Hauptschalter eingeschaltet wird. Dies ist der kritische Prozess einer Totempole-PFC, die mit der hohen Qrr der Substratdiode von Hochspannungs-Si-MOSFETs zu abnormalen Spitzen, Instabilität und damit verbundenen hohen Schaltverlusten führt. Der niedrige Qrr der GaN-Schalter ermöglicht es den Entwicklern, diese Barriere zu überwinden.

Entwickler können den Betrieb der Schaltung mit dem brückenlosen 4 kW Totempole-PFC-Evaluierungsboard TDTTP4000W066C von Transphorm untersuchen. Es verwendet als Controller den MA330048 (dsPIC33CK256MP506 Digital Power Plug-in Modul (PIM)) von Microchip Technology. Eine sehr hohe Effizienz der einphasigen Umwandlung wird mit den GaN-FETs TP65H035G4WS der Generation IV (SuperGaN) von Transphorm erreicht. Die Verwendung von GaN-FETs im schnell schaltenden Teil der Schaltung und niederohmigen MOSFETs im langsam schaltenden Teil der Schaltung führt zu verbesserter Leistung und Effizienz.

Bidirektionale Totempole-PFC kombiniert Silizium-FETs und SiC-FETs

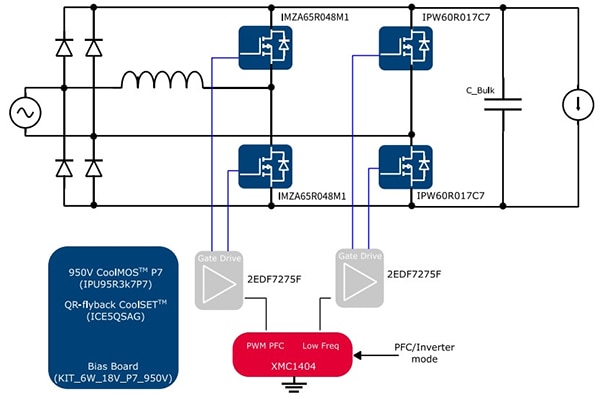

Für Entwickler von netzinteraktiven batterieelektrischen Fahrzeugen und batteriebasierten Energiespeichersystemen bietet Infineon mit dem Evaluierungsboard EVAL3K3WTPPFCSICTOBO1 einen 3300 Watt starken Totempole-PF-Korrektor mit bidirektionaler Leistung an (Abbildung 9). Dieses brückenlose Totempole-PFC-Board liefert eine hohe Leistungsdichte von 72 Watt pro Kubikzoll. Der auf dem Board EVAL3K3WTPPFCSICTOBO1 implementierte Totempole arbeitet sowohl im Gleichrichter- (PFC) als auch im Umrichterbetrieb in CCM, wobei die vollständige digitale Regelung mit dem Infineon-Mikrocontroller XMC1000 implementiert ist.

Abbildung 9: Ein Blockdiagramm des 3300 Watt Totempole-PFC-Evaluierungsboards EVAL3K3WTPPFCSICTOBO1 zeigt die Topologie, die die spezifizierte Leistungsdichte der Platine von 72 Watt pro Kubikzoll liefert. (Bildquelle: Infineon Technologies)

Abbildung 9: Ein Blockdiagramm des 3300 Watt Totempole-PFC-Evaluierungsboards EVAL3K3WTPPFCSICTOBO1 zeigt die Topologie, die die spezifizierte Leistungsdichte der Platine von 72 Watt pro Kubikzoll liefert. (Bildquelle: Infineon Technologies)

Diese Totempole-PFC verwendet eine Kombination aus Infineons 64mΩ-CoolSiC-SiC-MOSFETs IMZA65R048M1 für 650 Volt und seinen 17mΩ-CoolMOS-C7-Silizium-Leistungs-MOSFETs IPW60R017C7 für 600 Volt. Der Wandler arbeitet ausschließlich bei einer hohen Netzspannung (mindestens 176 Volt rms, nominal 230 Volt rms) in CCM mit einer Schaltfrequenz von 65 kHz und erreicht einen Wirkungsgrad von bis zu 99% bei halber Last. Weitere Infineon-Komponenten, die in dieser 3300 Watt starken bidirektionalen (PFC-AC/DC und Inverter-AC/DC) Totempole-Lösung verwendet werden, sind

- Isolierte Gate-Treiber 2EDF7275FXUMA1

- QR-Sperrregler ICE5QSAGXUMA1 mit einem CoolMOS-P7-MOSFET IPU95R3K7P7 für 950 Volt für die Bias-Hilfsspannung

- Mikrocontroller XMC1404 für die Implementierung der PFC-Regelung

Fazit

Ein niedriger PF führt zu Ineffizienzen im Versorgungsnetz und in Stromrichtern, so dass die PFC für eine Vielzahl von netzstrombetriebenen Wechselstromgeräten erforderlich ist, wobei Vorschriften für bestimmte Arten von elektronischen Geräten Mindest-PF-Werte vorschreiben. Um diese regulatorischen Anforderungen zu erfüllen und gleichzeitig den Bedarf an kleineren Formfaktoren und höherer Leistung zu erfüllen, benötigen Entwickler eine Alternative zu einfachen und kostengünstigen passiven PFC-Techniken.

Wie gezeigt, können Entwickler stattdessen aktive PFC-Designs unter Verwendung digitaler Regelungstechniken und WBG-Halbleitern wie SiC und GaN implementieren, um höhere PFs und kompaktere Designs zu erzielen.

Empfohlene Lektüre

Haftungsausschluss: Die Meinungen, Überzeugungen und Standpunkte der verschiedenen Autoren und/oder Forumsteilnehmer dieser Website spiegeln nicht notwendigerweise die Meinungen, Überzeugungen und Standpunkte der DigiKey oder offiziellen Politik der DigiKey wider.